采用CPLD/FPGA的VHDL语言电路优化原理设计

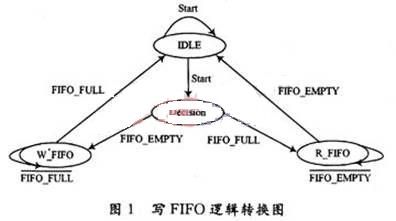

比较容易地设计出高性能的时序逻辑模块,在超声探伤数据采集卡的CPLD程序设计中,使用有限元状态机(FSM)设计CY7CA225 1K×16 b FIFO芯片的读写控制模块,并且达到很好的效果,逻辑转换图如图1所示。实践证明,实现相同的逻辑功能,使用状态机设计能使设计的电路得到更好的优化。

1.4 资源共享

资源共享的思想是通过使用数据缓冲器或多路选择器等方法来共享数据通道中占用资源较多的模块,如算法单元。通过共享电路单元模块可有效提高芯片内部资源的利用率,达到优化电路的目的。

1.5 利用E2PROM芯片节省片内资源

在用VHDL进行项目开发的过程中,经常需要存储一些配置参数值。理论上讲,每存储一个字节的配置参数需要使用8个CPLD宏单元,因此在CPLD内部存储这些参数并不是好的方案,除非使用的CPLD芯片已集成了E2PROM存储单元。例如,在设计超声探伤系统的数据采集卡的过程中,每个通道的采样数都需要保存在CPLD里面。由于项目初期芯片选型不当,选择一款EPM7192S160-15,该款芯片内部只有192个宏单元,因此考虑把参数存储在外扩的E2PROM芯片24WC02中。经实验证明,在CPLD内部实现一个I2C控制器仅需要43个宏单元。由此可见,当初始化参数大于5个的时候,通过外扩E2PROM芯片来存储配置参数是可行的,只需在CPLD/FPGA芯片内实现I2C控制器即可方便地读写E2PROM存储芯片。

2 结语

使用VHDL进行CPLD/FPGA电路设计时,要根据实际项目的具体情况,合理地划分项目功能,并用VHDL实现相应的功能模块。用模块来构建系统,可有效地优化模块间的结构和减少系统的冗余度,并在模块设计过程中始终贯彻以上的优化设计原则,借助于强大的综合开发软件进行优化,才能达到最优化电路的目的。

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)

- 基于CPLD的MIDI音乐播放器的设计(06-16)

- 基于CPLD的电器定时开关控制系统设计(08-17)

- 基于CPLD和VS1011E解码器的电梯语音系统设计(11-26)

- 基于DSP和CPLD的软开关电源数字控制器(01-14)

- ADS8323与高速FIFO接口电路的CPLD实现(03-26)