串行外围接口SPI功能模块的设计

SPI的状态寄存器来获取其所处的状态,从而决定下一步动作。

DMA方式由DMA模块控制数据在内存和SPI间的交换,而不需要处理器核的参与,有效提高了总线利用率。

外部MCU可以通过和内部MCU通讯的方式,把从模式的SPI配置成可以解析命令的模式,这样外部主模式的SPI可以在SSN低电平的时候连续传输多位数据,在下降沿的第一个数据被认为是命令。从模式的SPI可以解析这些命令然后做相应的操作。这些操作主要包括,清除接收FIFO或者发送FIFO中的数据,选择MCU或者DMA来作为数据交互的对象等,可以大大节省和MCU交互所需要的带宽。

作为主要组成部分的寄存器控制模块和SPI核心模块采用同步电路设计,它们之间的通讯采用异步电路设计。这些主要是考虑到SPI的带宽通过MCU的控制是可调的。SPI核心部分的时钟频率可调,可实现多种带宽,增加了本设计SPI的灵活性。

3.3 电路实现

为了保证RTL代码的正确性,对IP的功能进行全面的仿真验证。仿真包括RTL级和门级仿真验证。RTL级仿真是将代码文件调入硬件描述语言的仿真软件进行功能仿真,门级仿真包括布局布线前和布局布线后仿真。布局布线后仿真,获得精确的时延参数。将RTL级代码转换成门级网表,0.13um工艺标准单元库。

在传统的设计流程中进行功能验证,首先需要通过写测试矢量的方式给需要进行功能测试的模块加激励,然后通过观察模块的输出结果,判断模块的功能是否正确。但是在写测试矢量时,测试工程师是在自己对模块功能理解的基础上进行的。这样就存在一个问题,测试矢量对模块的激励有可能是不完备的,还有可能是错误的,但测试矢量的激励并没有使错误体现出来;也有可能模块的功能是正确的,误报错误使验证过程变得非常低效。为避免以上问题,对本设计模块的功能验证中,采用系统级验证环境。该环境由IP总线、驱动器、监视器、外部模块和协调它们工作的脚本组成。组成系统的各模块可以按需要加人环境。每次验证过程就是相应的激励作用于环境的过程。验证结果由环境产生、检验和输出。以保证测试矢量的完备性和正确性。

该验证环境在LINUX操作系统下,仿真器采用Cadence公司的Nc-verilog,支持C/C++、Verilog和VHDL协同仿真,可以直接把SPI模块挂在验证环境中,通过Verilog的$readmemh任务读入软件激励进行验证。

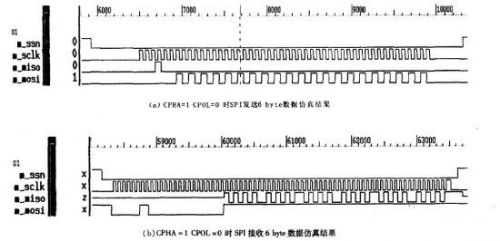

在系统时钟为36MHz的情况下,图5(a)给出了CPOL=0,CPHA=1时,发送6位数据的仿真结果。图5(b)给出了在CPOL=0,CPHA=0的情况下,接收6位数据的仿真结果。

图5 仿真结果

这两个仿真结果说明本设计完全支持4种SPI传输协议,而且能够以最大的速率无缝传输数据。

4 结束语

本设计的SPI可作为IP核嵌入监控系统SOC芯片中。芯片通过流片验证,各项指标已达到了原设计的要求,通过板级测试,芯片中SPI能支持4种传输协议,工作的最高频率可达18M bps,在一秒钟内能够抓图或者回显l5帧图像,达到业内较高水平。本设计中的不足之处是没有做数据校验,随着市场需求的提高,可在设计中增加CRC校验以增加数据的正确性,提高系统效率。

- PC机扩展RS-232接口(01-25)

- 串行及并行A/D转换器在高速数据采集中的采样差别性分析(05-19)

- 高速串行接口特征与应用(05-20)

- 嵌入式测试为串行I/O提供真正的价值(05-26)

- 串行通讯转接口类型 PowerChute Plus for Unix(06-08)

- 同步队列串行接口QSPI的研究与应用(09-21)