高频功率转换器的光耦合器及反馈回路

长久以来,设计功率转换器的挑战层出不穷,主要原因之一即在于电路板的空间有限。若要缩小转换器的外型尺寸,就必须提高频率。这样做能够使用较小的元件。通过将切换频率提高及让转换器的实体尺寸缩小,整体的效率需求也会提高。

输出电压降低时,功率级会增加,让负载的频率速度得以加快,这会造成输出电流量提高。当负载以较高的频率动态变化,控制回路必须保持不变。即使采用所有这些节省空间的规划,未来在功率转换器的设计上仍有其他挑战。

其中一项挑战是控制回路。若要处理更高的负载动态(load dynamics),并善用更小的元件优势,就需要更快速的控制回路。对于过去较慢的切换频率来说,3kHz的范围已经够好了,但当切换频率增加到200kHz以上,设计人员就会需要在比3kHz范围还大很多的频率下交越0dB增益点。对于最不理想的线路及负载条件,200kHz供应的上限(根据可接受的理论值)为40kHz。

以此相对较高的频率交越0dB增益,可让设计人员使用较小的输出电容,即使较高动态负载出现变化也是这样。这是因为当增益交越(gain crossover)提高,转换器的响应会加快,而且输出电容不需要在负载瞬时期间长时间保持电压。控制电路会调整传输功率,以补偿及控制输出电压,而且不需要仰赖输出电容来对负载或线路瞬时进行控制。此外,磁性元件因为切换频率增加而缩小,因此节省更多的空间。

当然,其中也有一些缺点。使用传统的电路时,切换耗损会增加,不过,设计更精良的元件已大幅减少切换耗损。

使用准谐振拓朴,例如含UCC3895之类控制器的相移全桥式拓朴,有助于减少切换耗损。在许多设计中,二次侧的同步切换所产生的效用相当显著。

磁性元件、开关及输出电容都会以频率函数关系来影响控制对输出的增益。反馈控制有其本身的挑战,而且反馈电路的寄生电容是更为重要的因素。

在这些较高的频率下,寄生电容成为一大问题。进行低频率切换时,0dB交越约在5kHz或5kHz以下的频率附近,而反馈回路中的寄生电容主要与配置有关。然而,当进行30kHz交越设计时,会有其他因素造成问题,其中一项因素便是本文的主题。

最近笔者在一个转换器上遭遇到这个特殊的问题,这个转换器以400kHz运作,并且采用一次侧使用控制IC(UCC3895)而二次侧感应输出的相移设计。

设计人员当初使用光耦合器来跨越一次侧对二次侧的隔离阻障,一开始似乎一切都已经考虑周详,不过,回路因为某种原因而变得不稳定,而且在维持DC设定点时,输出发生低程度的振荡。

当然我们的设计人员检查过计算过程,但是没有发现任何明显的因素。然后,设计人员将转换器设定为在出现AC链波的DC状态下保持稳定,并且开始探究电路。

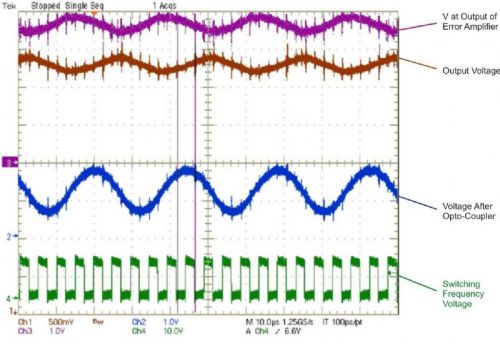

经过一段长时间的努力,发现虽然二次侧的错误放大器确实重现了出现在转换器输出端的涟波,并具有正确的180度相位变化,但来自光耦合器的信号却比频率约为35 kHz的预期相位偏移了大约45度。这足以移除交越的相位容限(phase margin),而导致所观测到的振荡。图1显示这三个波形。

图1 显示通过光耦合器的相移

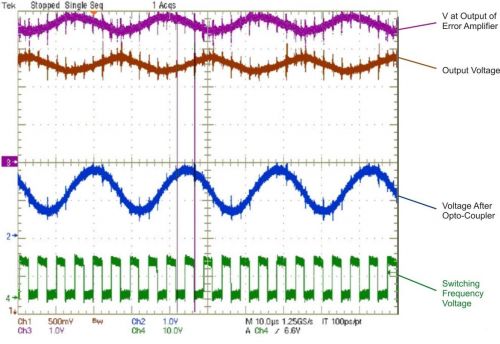

光耦合器数据表未提及这一相移,但发现这样的效应使得设计人员想起光耦合器会在较高频率的情况下产生极点。在查阅不同光耦合器的数据表后,并未发现其中提及因为频率作用所造成的相移。于是进行了进一步调查,并制作一个测试电路来检查整个光耦合器之中增益与相位的关系。图2显示此电路,其中使用网络分析仪来测量数据。

图2 用来获得通过受测光耦合器的增益与相位的测试电路。

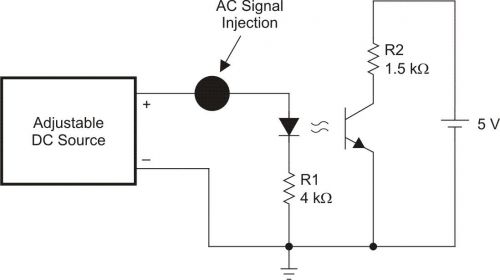

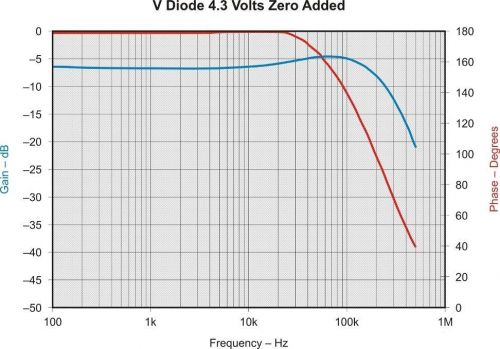

设计人员使用图2显示的电路进行第一次测试,然后针对通过电阻器时所产生的相位和增益,绘制出相关于频率的变化图。图3为测试的结果,而此测试在可调变的DC电源端使用的是4.3伏特的电压。设计人员使用跨越R1和R2的电压来建立这些相移。

图3 光耦合器受测回路的相位和增益相关于频率的关系图

当相移45度且增益下降3dB时,极点的频率约为35kHz,这便解释了之前观测到的现象。这个耦合器在我们关心的频率之外,也出现其他复杂的极点与零点,不过与此分析没有关联,于是不加理会。

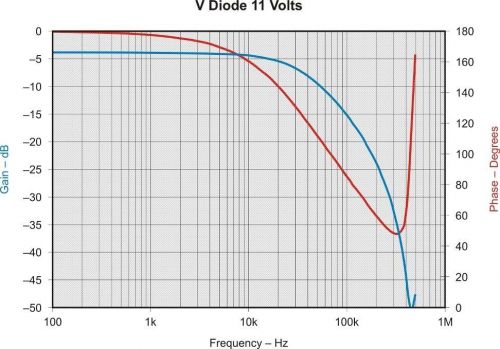

设计人员将测试电路的DC电压增加到11V,并且重复测量类似的结果。极点并未随着光耦合器的增大电流而明显变化。

图4 光耦合器较高电流的相位/增益测试

接着设计人员尝试在4kΩ电阻加上1.2nF电容,以补偿极点。设计人员依序在两个电流量重复相同的测试,而这在35kHz产生零点,有助于补偿光耦合器的极点。

图5 在35 kHz增加零点的结果

在这两种情况下,这作法都能有效地移动相移,当频率超过100kHz时,它会跨越135度的相移点,并在超过200kH

- 一种智能高频开关电源监控模块的设计 (03-09)

- 高频电源变压器磁芯的设计原理(10-26)

- 高频电源模块的驱动电路的设计与研究(05-06)

- 高频开关电源的EMC设计(05-22)

- 高频链逆变器的重复控制策略研究(05-26)

- 高频电源模块缓冲电路优化探讨(10-07)