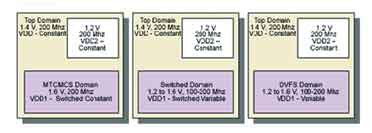

图3 各类的多电压域(multi-Vdd)设计

在将设计分成多个电压岛时,网表中必须要插入适当的电压转换元件来从一个电压域到另一个电压域连接信号。一个真正有功率意识的设计环境应该能够自动插入这些单元。

功率门控(Power gating)

功率门控通过有选择地切断设计中未在使用部分的电源来解决泄漏问题,如图4所示。它是利用高阈值电压(high-Vt)开关来连接全局恒定电源线轨与局域开关电源线轨,这就使得局域线轨的供电能根据需要开启或者关闭,提供了细粒度、中粒度和粗粒度控制能力。

图4 分布式多阈值CMOS(MTCMOS)

其他技术则均得益于具有"功率意识",例如:映射、利用非关键时序路径的多阈值晶体管、平面规划和布局、解耦电容布局、时钟树综合和时钟门控,以及时序优化。

总之,功率分布网络应基于早期功率网格还没有完成时执行的线轨分析结果进行设计。芯片上正确的消耗元件分布应避免热点和局部电压降问题,线宽算法能够有效解决电压降和电迁移问题。

集成的工具套件

目前,第三方单点工具要么需要使用到多个数据库,要么需要将完全不同的数据模型组合进一个数据库中,不仅需要执行数据转换和文件传输,同时也使得数据管理工作变得相当烦琐、耗时且容易出错。

然而,最严重的问题还在于,其布局后再修正缺陷的做法代价极为昂贵,特别在修正工作必须手工进行时就更是如此。如果在手工修正之后必须返回重新进行分析工作(而不是与修正工作同时进行),那么情况将会进一步恶化,因为分析后可能显示出修正工作要么未起到应有的作用,要么可能给设计工作带来了新的、不一样的缺陷。

例如:要想完全计算出电压降效应的影响,首先重要的是要拥有一个能基于实际电压降以单元为基础地进行时序衰减计算的环境;接着,时序分析引擎应利用这种衰减后时序数据来识别关键路径上的潜在变化;最后,优化引擎应进行适当的修正来解决由于时序变化而导致的潜在的建立或保持问题。

而这就需要有一个能够确保功率分析、电压降分析、衰减计算、时序分析和优化引擎可无缝协作的设计环境。

功率分析单点工具与环境的其他部分之间集成性的缺乏意味着当功率分析结果用于定位和隔离时序和/或信号完整性问题时,修正问题的同时也将给功率网络引入新的问题,最终可能导致大量、耗时的设计迭代。

一个真正的低功耗设计环境应具备让所有的功率分析工具与综合、布局布线、时钟树综合、提取、时序和信号完整性分析等实施工具同时运行的特性,要能够使用统一数据模型来为这些工具提供对分析数据的同步访问并实现对设计的"实时"变更。

结束语

要想完全优化低功耗设计,功率分析工具必须彼此间完全集成,同时还要能与流程中的其他实施和分析引擎相集成,包括综合、布局布线、电压降衰减、时序、优化和信号完整性分析引擎。

这样的架构使得所有实施和分析引擎都能够通过统一数据模型同时访问到设计数据,而且通过一个工具所做出的任意变更可立即得到其他工具的测试和验证。从而最终形成一种收敛算法,无须采用耗时的迭代即可快速确定最佳解决方案。

发布者:博子 | |