基于LFSR优化的BIST低功耗设计

时间:08-10

来源:国外电子元器件

点击:

引言

随着便携式设备和无线通讯系统在现实生活中越来越广泛的使用,可测性设计(DFT)的功耗问题引起了VLSI设计者越来越多的关注。因为在测试模式下电路的功耗要远远高于正常模式,必将带来如电池寿命、芯片封装、可靠性等一系列问题。随着集成电路的发展,内建自测试(BIST)因为具备了诸多优越性能(如降低测试对自动测试设备在性能和成本上的要求、可以进行At-speed测试及有助于保IP核的知识产权等),已成为解决SoC测试问题的首选可测性设计手段。

在BIST中常用线性反馈移位寄存器(LFSR)作为测试模式生成器(TPG)。LFSR必须产生很长的测试矢量集才能满足故障覆盖率的要求,但这些矢量消耗了大量的功率。

另外,在系统工作模式下,应用于给定电路的连续功能输入矢量具有重要的相关性,而由LFSR产生的连续测试模式之间的相关性很低。因此,在自测试期间会增加电路中节点的翻转活动,导致功耗增大。

2 功耗分析和WSA模型

CMOS电路中功耗的来源主要分为静态功耗和动态功耗两种。漏电流或从电源供给中持续流出的其它电流导致静态功耗。动态功耗则是因为短路电流和负载电容的充放电,从而由电路正常工作时的功能跳变所引起的,它包括功能跳变、短路电流、竞争冒险等。对于CMOS工艺来说,目前动态功耗是电路功耗的主要来源。

对于节点i上每次开关上的功耗为:

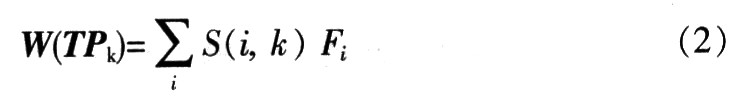

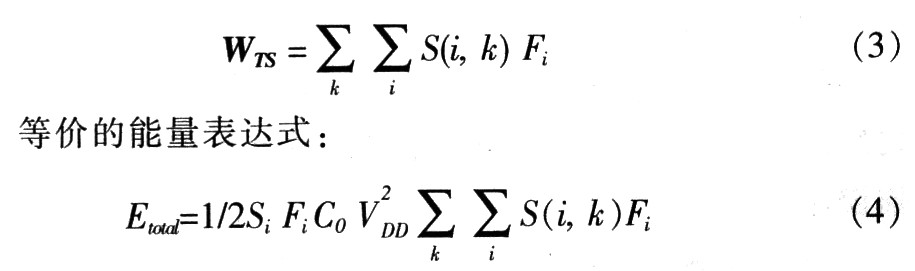

从式(1)看出,门级的功耗估计与Si和Fi的乘积和节点i的翻转次数有关。节点的扇出由电路拓扑决定,而它的翻转次数由逻辑模拟器来估计。这个乘积即称为节点i的权重翻转活动(Weighted Switching Activity,WSA)。在测试过程中WSA是节点i功耗Ei的唯一变量,所以WSA可作为该节点的功耗估计。对于一对连续的输入矢量TPk=(Vk-1,Vk),电路总的WSA为:

根据式(2),考虑长度为L的测试矢量TS作为电路的输入矢量,电路总的WSA为:

(1)电路中节点i的跳变数成为唯一的影响能量、最大功耗和平均功耗的参数。

(2)测试中时钟的频率也影响着平均功耗和最大功耗。

(3)测试长度,即施加在待测电路(CUT)上的测试向量的数目一只影响总的能量的消耗。

3 LFSR优化的低功耗方法

通过对测试过程的功耗分析可知,选择BIST低功耗的方案时,一方面可以通过减少测试序列长度来实现(但该方法往往以牺牲故障覆盖率为代价),另一方面降低WSA值也可实现系统功耗的降低。

在BIST结构中,线性反馈移位寄存器(LFSR)由于结构的简单性、规则性、非常好的随机测试矢量生成特性、用来压缩测试响应时的混淆概率非常小等特点,在DFT的扫描环境中很容易集成,所以当从扫描DFT设计升级成BIST设计时,LFSR因其硬件开销很小而成为BIST中应用最广的矢量生成结构。

基于LFSR优化的BIST结构可分为test-per-一scan和test-per-clock两类结构。test-per-scan技术引起的面积开销较小,测试结构简单,易于扩展:而test-per-clock在一个周期内可实现矢量的生成和响应压缩,能够完成快速的测试。

3.1 基于扫描的test-per-scan方式

3.1.1 基本结构

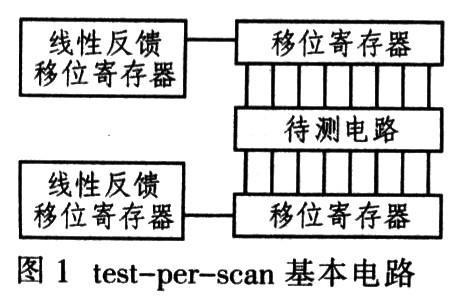

test-per一scan内建自测试的目标是尽可能的降低硬件开销。这种结构在每个输入输出端口处使用LFSR与寄存器的组合来代替LFSR。图l是test-per-scan内建自测试的基本电路结构。在内建自测试矢量下,LFSR生成测试矢量并且通过扫描移位寄存器(shift register)将测试矢量移位到待测电路(CUT)的输入端,同时响应被移入LFSR并压缩。

全扫描或部分扫描设计中由于移位会产生比较大的功耗。基于扫描的test一per-scan低功耗设计方法需要修改标准的扫描设计,降低状态转换活动率。没计修改包括在移位期间用于屏蔽扫描路径活动的一些门控逻辑,以及对用于抑制随机模式的附加逻辑进行综合等。

3.1. 3 部分扫描算法

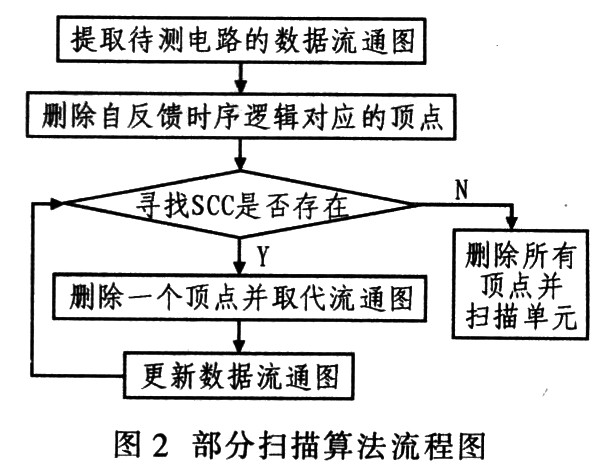

根据以上扫描设计原理,在消除测试序列中的冗余模式之后,采用图2所示的部分扫描算法对待测电路进行部分扫描设计。其步骤如下:

①首先删除所有自反馈时序逻辑对应的顶点。

②在数据流图中查找所有的强连通单元(Strongly Connected Components,简称SCC)。

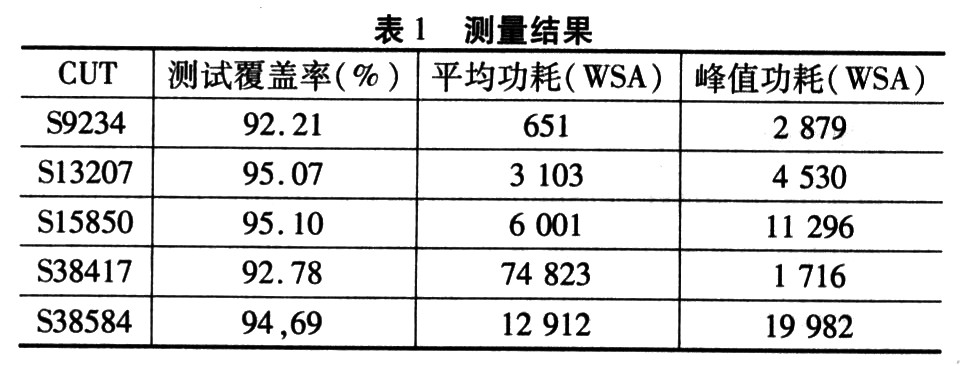

参考文献采用上述算法对ISCA89基准电路扫描BIST测试,并采用ATPG工具和仿真工具VCS故障模拟和功能模拟,表1列出测试覆盖率、平均功耗和峰值功耗数据。

随着便携式设备和无线通讯系统在现实生活中越来越广泛的使用,可测性设计(DFT)的功耗问题引起了VLSI设计者越来越多的关注。因为在测试模式下电路的功耗要远远高于正常模式,必将带来如电池寿命、芯片封装、可靠性等一系列问题。随着集成电路的发展,内建自测试(BIST)因为具备了诸多优越性能(如降低测试对自动测试设备在性能和成本上的要求、可以进行At-speed测试及有助于保IP核的知识产权等),已成为解决SoC测试问题的首选可测性设计手段。

在BIST中常用线性反馈移位寄存器(LFSR)作为测试模式生成器(TPG)。LFSR必须产生很长的测试矢量集才能满足故障覆盖率的要求,但这些矢量消耗了大量的功率。

另外,在系统工作模式下,应用于给定电路的连续功能输入矢量具有重要的相关性,而由LFSR产生的连续测试模式之间的相关性很低。因此,在自测试期间会增加电路中节点的翻转活动,导致功耗增大。

2 功耗分析和WSA模型

CMOS电路中功耗的来源主要分为静态功耗和动态功耗两种。漏电流或从电源供给中持续流出的其它电流导致静态功耗。动态功耗则是因为短路电流和负载电容的充放电,从而由电路正常工作时的功能跳变所引起的,它包括功能跳变、短路电流、竞争冒险等。对于CMOS工艺来说,目前动态功耗是电路功耗的主要来源。

对于节点i上每次开关上的功耗为:

从式(1)看出,门级的功耗估计与Si和Fi的乘积和节点i的翻转次数有关。节点的扇出由电路拓扑决定,而它的翻转次数由逻辑模拟器来估计。这个乘积即称为节点i的权重翻转活动(Weighted Switching Activity,WSA)。在测试过程中WSA是节点i功耗Ei的唯一变量,所以WSA可作为该节点的功耗估计。对于一对连续的输入矢量TPk=(Vk-1,Vk),电路总的WSA为:

根据式(2),考虑长度为L的测试矢量TS作为电路的输入矢量,电路总的WSA为:

(1)电路中节点i的跳变数成为唯一的影响能量、最大功耗和平均功耗的参数。

(2)测试中时钟的频率也影响着平均功耗和最大功耗。

(3)测试长度,即施加在待测电路(CUT)上的测试向量的数目一只影响总的能量的消耗。

3 LFSR优化的低功耗方法

通过对测试过程的功耗分析可知,选择BIST低功耗的方案时,一方面可以通过减少测试序列长度来实现(但该方法往往以牺牲故障覆盖率为代价),另一方面降低WSA值也可实现系统功耗的降低。

在BIST结构中,线性反馈移位寄存器(LFSR)由于结构的简单性、规则性、非常好的随机测试矢量生成特性、用来压缩测试响应时的混淆概率非常小等特点,在DFT的扫描环境中很容易集成,所以当从扫描DFT设计升级成BIST设计时,LFSR因其硬件开销很小而成为BIST中应用最广的矢量生成结构。

基于LFSR优化的BIST结构可分为test-per-一scan和test-per-clock两类结构。test-per-scan技术引起的面积开销较小,测试结构简单,易于扩展:而test-per-clock在一个周期内可实现矢量的生成和响应压缩,能够完成快速的测试。

3.1 基于扫描的test-per-scan方式

3.1.1 基本结构

test-per一scan内建自测试的目标是尽可能的降低硬件开销。这种结构在每个输入输出端口处使用LFSR与寄存器的组合来代替LFSR。图l是test-per-scan内建自测试的基本电路结构。在内建自测试矢量下,LFSR生成测试矢量并且通过扫描移位寄存器(shift register)将测试矢量移位到待测电路(CUT)的输入端,同时响应被移入LFSR并压缩。

全扫描或部分扫描设计中由于移位会产生比较大的功耗。基于扫描的test一per-scan低功耗设计方法需要修改标准的扫描设计,降低状态转换活动率。没计修改包括在移位期间用于屏蔽扫描路径活动的一些门控逻辑,以及对用于抑制随机模式的附加逻辑进行综合等。

3.1. 3 部分扫描算法

根据以上扫描设计原理,在消除测试序列中的冗余模式之后,采用图2所示的部分扫描算法对待测电路进行部分扫描设计。其步骤如下:

①首先删除所有自反馈时序逻辑对应的顶点。

②在数据流图中查找所有的强连通单元(Strongly Connected Components,简称SCC)。

参考文献采用上述算法对ISCA89基准电路扫描BIST测试,并采用ATPG工具和仿真工具VCS故障模拟和功能模拟,表1列出测试覆盖率、平均功耗和峰值功耗数据。

由表l数

由表l数

- 实用模拟BIST的基本原则(07-08)

- 模拟BIST的四项基本原则(02-12)

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 如何将CMOS LDO应用于便携式产品中(01-15)