基于CPLD的VGA视频显示系统的设计

时间:05-16

来源:EDN

点击:

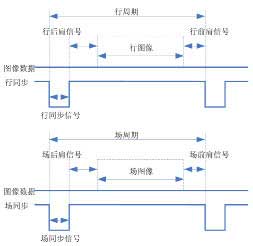

| 图6 缓冲模块通信软件流程图 VGA时序发生器设计 VGA标准时序参考图如图7所示,并用VERILOGHDL设计For VESA 800*600 @ 60Hz:VGA时序的源代码:

|

- VGA旌接RCA接口转换器(04-05)

- 针对EDGE/GSM手机发送电路的四种架构分析(03-21)

- 数字控制式VGA(06-26)

- 可编程放大器解决可变增益放大瓶颈问题(10-05)

- 两款新器件重塑信号发生器(03-16)

- 轻松使用HDMI:HDMI-VGA和VGA-HDMI转换器(03-30)