一种基于CMOS工艺的电荷泵锁相环芯片的设计

时间:05-21

来源:EDN 作者:武汉科技大学 冯伟平

点击:

2.4 环路滤波器

环路滤波器具有低通特性,在锁相环中起到低通滤波的作用,而且它对整个环路系统的参数设计起着决定性的作用。本设计采用二阶无源低通滤波器,详见文献[3]所述。

本系统所设计的锁相环可广泛应用于电源电压为5 V时,锁相环捕捉带为41~110 MHz,3 V时捕捉带则为25~58 MHz。由文献[5]中所述,该系统采取的是电压型电荷泵,将电压型转换为电流型,查出内部MOS饱和导通,保证UP和DN为恒压源的最大导通电流,可得 R1。以电源电压为5 V,忽略分频环节为例,可以得到:

3 仿真结果

采用0.5μm工艺库,Cadence Spectre工具对本文所设计的锁相环设计可以得到下列结果:

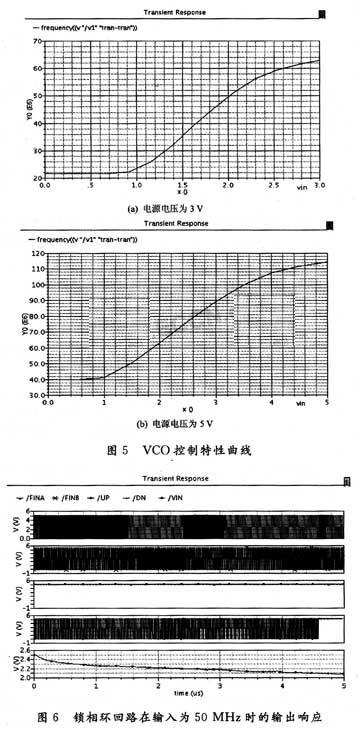

图5(a)是电源电压为3 V时的VCO控制特性曲线,有效工作范围为25~58 MHz,且线性度良好;图5(b)是电源电压为5 V时的VCO控制特性曲线,有效工作范围为41~110 MHz,且线性度良好。

另外通过对VCO起振过程的测量可知,起振时间很小,为63.5 ns。

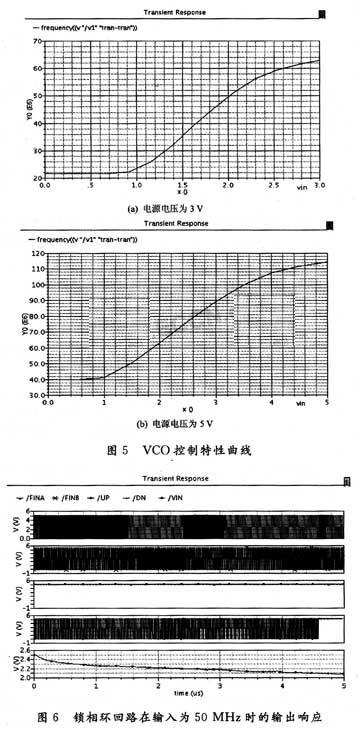

图6是锁相环回路在输入为50 MHz时的输出响应,锁定时间约为4.6μs。

4 结语

使用0.5 μm CMOS工艺实现5 V锁定范围为41~110 MHz,3 V时锁定范围为25~58 MHz的锁相环单片集成电路,经过分部仿真和总体系统仿真可知,运用本文所述方法设计二阶三型锁相环芯片各组成部分特性与理论相符,可以实现相位和频率的同步跟踪,且时域特性良好。

|