3D集成电路将如何同时实现?

高分子粘结键合

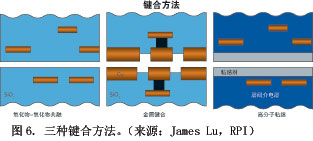

由于特征尺寸的限制,图6所示全部键合技术都需要特别光滑、平整和洁净的表面。尽管所有这些技术看起来都可行,但有一种趋势是转向使用金属-金属键合技术,因为这种技术可以同时实现机械和电学的接触界面。铜-铜键合直接铜键合工艺需要到在350-400℃温度下施加压力超过30分钟,接着在350-400℃下的氮气气氛退火30-60分钟。这一工艺需要高度抛光的铜表面并保持很高的洁净度。像EVGroup(奥地利St.Florian/Inn)和SUSSMicroTec(佛蒙特州,Waterbury)等厂商提供的商业化工具,需要在单个对准工具上装有多个键合头,才能得到可接受的产能。一种像Ziptronix(北卡罗来纳州,Morrisville)报道的称作直接键合互连(DBI)的工艺,据说可以大大提高这一产能。这种技术使用金属对TSV进行封帽,之后采用氧化物、金属同步CMP进行平坦化,经过专利保护的表面处理技术,可使用标准的键合/对准机在大气环境下1-2分钟内实现芯片或者晶圆的键合。在350℃温度下施加压力,在低CoO键合操作下可以获得了单一的金属界面。

表2总结了九种不同的3D集成工艺流程,都对应从晶圆工艺一直到键合。

References

1. A. Braun, "Low-k Bursts Into the Mainstream…Incrementally," Semiconductor International, May 2005, p. 41.

2. K. Saraswat, "3D IC's: Motivation, PeRFormance Analysis and Technology," 3D Architectures for Semiconductor Integration & Packaging, Phoenix, June 2005.

3. S. Vitkavage and K. Monnig, "3D Interconnects and the IRTS Roadmap", Proc. 3D Architecture for Semiconductor Integration and Packaging Conf., Phoenix, 2005.

4. J.A. Davis et al., "Interconenct Limits on Gigascale Integration in the 21st Century", Proc. IEEE, Vol. 89, 2001, p. 305.

5. P. Garrou, "3D Integration Invades Whitefish Montana," Perspectives From the Leading Edge, Sept. 7, 2007.

6. P. Morrow et al., "Design and Fabrication of 3D Microprocessors," MRS Proc., Vol. 970, Enabling Technologies for 3D Integration, C.Bower, P. Garrou, P. Ramm, K. Takahashi Eds., 2007, p. 91.

7. P. Garrou, "Future ICs Go Vertical," Semiconductor International, February 2005, p. SP10.

8. P. Garrou, "3D IC Integration: Evolution or Revolution?", Perspectives From the Leading Edge, March 16, 2008.

9. P. Garrou, "ASET Drives 3D Integration Workshop in Tokyo," Perspectives From the Leading Edge, June 21, 2008.

10. P. Garrou, "Going Vertical in Whitefish," Sept. 9, 2007; "High Throughput Laser Drilling for 3D IC TSV," Feb. 17, 2008, Perspectives From the Leading Edge.

11. P. Garrou, "3D Equipment & Materials Vendors Consortium," Perspectives From the Leading Edge, Aug. 26, 2007.

12. P. Garrou, "3D Practitioners Assemble at Fort McDowell," Perspectives From the Leading Edge, March 23, 2008.

13. P. Garrou, "NXP Proposes Passive Integration in 3D IC Stacks," Perspectives From the Leading Edge, April 13, 2008.

14. P. Garrou, "More 3D Integration at ECTC 2008," Perspectives From the Leading Edge, June 28, 2008.

15. P. Garrou, "If It's Thursday It Must Be San Jose," Perspectives From the Leading Edge, June 8, 2008.

16. D.M. Jang et al., 57th Electronic Component Tech. Conf. 2007, p. 847.

17. P. Garrou, "3D Road Tour Continued," Perspectives From the Leading Edge, May 28, 2008.

18. Handbook of 3D Integration, P. Garrou, P. Ramm & C. Bower Eds., Wiley-VCH.

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- 用于下一代移动电话的电源管理划分(08-28)

- 不同电源供电的器件间的桥接(04-27)