3D集成电路将如何同时实现?

减薄

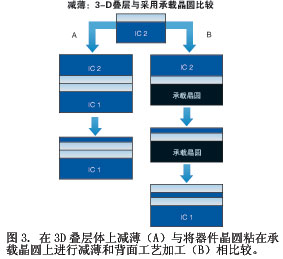

大多数3DIC工艺中,单个IC的厚度都远低于75μm。减薄器件晶圆有两种选择(图3)。在工艺A中,晶圆2以正面朝下的方式直接与IC叠层键合在一起。该晶圆接着被减薄到所需厚度,可能将TSV的背端露出。背面工艺顺序刻蚀出通孔(如果没在晶圆加工厂中实现的话),并制作出背面I/O焊盘。这样的叠层减薄也可以使用已知良好芯片(KGD)而非整个晶圆,以正面朝下的方式与芯片叠层键合。

在减薄和最终的背面工艺完成之后,器件晶圆可与叠层进行对准和键合,之后与承载晶圆分离(晶圆到晶圆键合),或者器件晶圆经由承载晶圆直接释放到划片框的划片胶带上,KGD可以进行后续操作。

对像存储器这样单片成品率高、芯片尺寸一致的晶圆来说,W2W是最合适的。D2W键合则是用于单片成品率低和/或芯片尺寸不同的晶圆。由于D2W键合之后就无法继续利用整片晶圆进行低成本加工的特性,因此何时完成D2W组装非常关键。

形成通孔

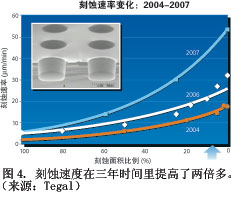

目前"钻蚀"TSV的技术主要有两种,一种是干法刻蚀或称博世刻蚀,另一种是激光烧蚀(表1)。博世工艺十多年为MEMS工业而开发,快速地在去除硅的SF6等离子刻蚀和实现侧壁钝化的C4F8等离子沉积步骤之间循环切换。通过图4可以看出,在过去几年里,刻蚀速度稳步提高。

对于激光技术的重大进展,三星(韩国,首尔)已经在存储器叠层中采用了这一技术。大多数最新数据都来自于Xsil(爱尔兰,都柏林)的AlexeyRodin及其同事。作为一种不需掩膜的工艺,激光加工避免了光刻胶涂布、光刻曝光、显影和去胶等工艺步骤。然而,未来当TSV尺寸降到10μm以下时,激光钻孔是否可以进一步缩小,目前来看还存在一些问题。

通孔绝缘

通常氧化物(SiO2)绝缘层可以使用硅烷(SiH4)或TEOS通过CVD工艺沉积获得。如果TSV在芯片制造之后进行绝缘和填充,则需要小心选择沉积温度。为获得具有合适密度的功能性绝缘层,典型的TEOS沉积温度在275-350℃范围。

诸如CMOS图像传感器和存储器等应用,则要求更低的沉积温度。Alcatel(近期刚被Tegal收购,加州Petaluma)和其他的一些设备制造商最近开发了这类低温氧化物沉积技术。IMEC(比利时鲁汶)曾报道使用Parylene前驱体,可以在室温下进行沉积,可作为TSV的高效有机绝缘层。

阻挡层、种子层和填镀

阻挡层、种子层和电镀技术的性能取决于通孔的尺寸和深宽比(AR)。不管是从制作盲孔方面考虑,还是从填孔方面考虑,清楚不同通孔尺寸下所需的深宽比要求非常重要。大多拥有成本(CoO)模型显示,通孔制作和通孔填充是3D集成的主要成本障碍,但这明显取决于通孔尺寸、节距和深宽比。尽管设备供应商和材料供应商正在努力研究10:1到20:1的深宽比,但在短期内,这样的深宽比将在何种应用中使用尚不明确。

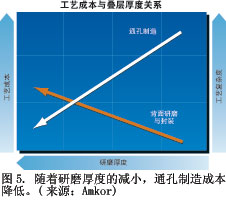

Amkor(亚利桑那州Chandler)的研究显示,使用较薄的电路层,结合较小尺寸的通孔,可以实现较低的CoO,因为这些深宽比较低的通孔对应制造成本较低(图5)。

诸如CMOS图像传感器、存储器、逻辑电路上存储器之类3D应用,在未来2-3代内都不会需要使用大于5的深宽比。在TSV尺寸降到约1μm甚至更小之前,我们将不会看到深宽比达到10-20范围。

铜通孔中,TiN粘附/阻挡层和铜种子层都通过溅射来沉积。然而,要实现高深宽比(AR>4:1)的台阶覆盖,传统的PVD直流磁控技术效果并不令人满意。基于离子化金属等离子体(IMP)的PVD技术可实现侧壁和通孔底部铜种子层的均匀沉积。由于沉积原子的方向性以及从通孔底部到侧壁溅射材料过程中离子轰击的使用,IMP提供更好的台阶覆盖性和阻挡层/种子层均匀性。

晶圆键合技术选择

针对3D集成而考察的晶圆键合技术包括:

氧化物(SiO2)共熔键合

金属-金属键合

铜-铜共熔键合

共晶键合(Cu/Sn)

凸点技术(Pb/Sn、Au、In)

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- 用于下一代移动电话的电源管理划分(08-28)

- 不同电源供电的器件间的桥接(04-27)