双路输出正激式DC/DC变换器的设计

时间:03-23

来源:中电网

点击:

5 磁复位设计

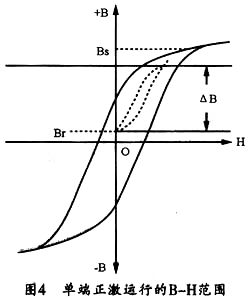

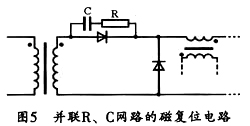

本电路中变压器的工作方式为单端正激式,变压器磁心工作在磁滞回线的第一象限,如图4所示,为了确保变压器在磁化曲线的线性区工作,设计时应在开关功率管截止期间将高频变压器复位,并使增长的磁通和减小的磁通平衡,以防止变压器磁芯饱利。

为达到降低输出纹波电压的目的,设计时,首先要减小功率开关管的电压尖峰。因为当VMOS管由导通变成截止时,在变压器的一次绕组上就会产生尖峰电压和感应电压,其中尖峰电压是由高频变压器漏感(即漏磁产生的自感)引起的,它与直流高压和感应电压叠加后很容易损坏VMOS管,故在设计时,要优化功率变压器的设计,减小变压器初级漏感;第二,电路布线时要尽量减少VMOS各端点的连接线长度,特别是栅极引线,如果无法使引线缩短,可以靠近栅极处串联一个小电阻,或者在漏级与地之间接上电容以减小振荡,减低尖峰电压;第三,应采用合适的RC吸收网络,以减小功率开关管的电压尖峰;此外,整流二极管在关断时的反向恢复时间也会导致尖峰电流,从而造成纹波,因此,设计时要优选反向恢复时间短的肖特基二极管来减小尖峰;最后,LC滤波电路要合理确定电感器的电感,应选用高可靠、温度性能好的高频独石电容为滤波电容,以减小纹波电压。

7结束语

本文介绍的双路输出正激式DC/DC变换器采用厚膜混合集成电路技术,裸芯片组装,金属全密封封装,同时采用平行封焊工艺来保证产品的高可靠性,表2所列是其电路性能参数由表2可见,该产品输出电压稳定,产品一致性好,同时具有体积小、重量轻、可靠性高、耐冲击、组装方便等优点,完全满足使用要求,可以应用于航空、航天、船舶等多项领域,以便为我国国防武器现代化提供保障。

- AD9958高性能可双路输出的DDS器件(02-16)

- 电磁探伤仪电源系统研究(09-22)

- 一种升压型PFM控制DC/DC转换器(11-11)

- 抑制电子设备中电磁干扰的产生来源(10-04)

- DC/DC模块的电源纹波测量(03-15)

- 一种基于三电平的单级PFC电路设计(12-03)