双路输出正激式DC/DC变换器的设计

时间:03-23

来源:中电网

点击:

0引言

开关电源以其高效率、小体积等优点已获得了广泛应用。而转换器是开关电源中最重要的组成部分,转换器有5种基本类型:单端正激式、单端反激式、推挽式、半桥式和全桥式转换器。在所有的DC/DC隔离变换器中,正激变换器是低电压大电流功率变换器的首选拓扑结构。由于正激变换器使用无气隙铁心,电感值高,原边和负边峰值电流小,铜损小,所以变压器利用率较高,输出效率也很高;其次,正激变换器中输出电感器和续流二极管的存在,也可以有效衰减纹波电流。为此,本文介绍了一种采用单端正激式结构设计的双路输出(%26#177;6 V,1.5 A)DC/DC变换器的设计过程。

1电路工作原理

本变换器的电路原理框图如图1所示。当直流输入电压经过滤波电路进入辅助电源后,即由辅助电源给控制器供电,然后在控制器作用下,用开关管控制电流的通断以形成高频脉冲电流,再经高频变压器,使其在输人为高(开关管接通)时整流二极管导通,从而使串联电感为充电状态,最后经滤波电路向负载传送能量并输出直流电压;相反,在输入低电平(开关管断开)时,电感为放电状态,电路将通过续流二极管继续向负载释放能量,并输出直流电压。为了保持电压稳定,两路输出电压经取样、隔离反馈电路送到控制器后将使输出脉冲宽度随输出电压的变化而变化,从而稳定输出电压。由于变压器原边绕组通过的是单向脉动电流,为避免磁性饱和,确保励磁磁通在每一个开关周期开始时处于初始值,设计时必须使变压器的铁芯磁性复位。

传统的开关电源普遍采用电压型脉宽调制(PWM)技术,而近年来,电流型PWM技术得到了飞速发展,本设计采用电流型控制器UC1843来实现控制回路。UC1843工作频率可达500 kHz,并它具有大电流推拉式输出,低启动工作电流等特点。电路中在开关管通断瞬间,必须供给栅极较大电流,并对栅源极间电容进行快速充放电,以使开关管高速工作。UC1843的输出级为图腾柱式,输出电流为1 A。它不必增加任何外围电路,就可将其直接接到开关管的栅极,并驱动VMOS管高速工作。UC1843具有精度高、电压稳定、外围电路简单优点。相比电压型PWM,电流型PWM具有更好的电压调整率和负载调整率,系统的稳定性和动态特性也有明显的改善。

3双路输出设计

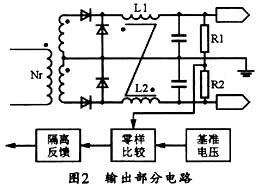

本设计中的双路输出部分电路如图2所示。

其次。也可将采样比较器R1、R2直接跨接到正负电源的输出端上。本设计的逻辑"地"不是电源的输出地.而是以负电压输出端作为采样比较和基准电压的逻辑"地"电位。这样,采样误差将同时反映出正、负2路输出的电压精度变化,并对正、负2路同样存在有反馈作用,以在很大程度上改进2路输出的调整率。

4变压器设计

开关电源的设计主要分为两部分,一是电路部分的设计。二是磁路部分的设计。开关电源变压器是高频开关电源的核心元件,必须进行合理设计才能达到理想效果。一般情况下,开关电源变压器的选用原则如下:

(1)要有较高的饱和磁通密度BS和较低的剩余磁通密度Br,以减少变压器的匝数和铜损。

(2)在高频率下应有较低的功率损耗;因为变压器高频工作时会发热而造成磁心损耗,从而影响电源输出效率,造成波形畸变等不良后果。

(3)适中的磁导率;不同的相对磁导率适合于不同的工作频率,比如相对磁导率为2000的材料,其适用频率在300 kHz~500 kHz。

(4)较高的居里温度;居里温度是使磁性材料失去磁特性时的温度。居里温度值过低,高温工作时会使磁心的饱和磁通密度严重跌落,从而影响正常工作。

为此,本电路根据工作频率、输出功率、模块体积等要求,选用磁心规格为PC40-P11/7Z-52H的TDK磁性材料。其参数见表1所列。

实际绕制变压器时,先根据计算所得的变压器匝数比,以绕满罐为原则来绕制变压器,再在电路中根据输出效率要求和工作电压范围,来观察开关管漏极上的电压波形,并对变压器匝数进行适当调整。事实上,当电源初次级匝数比增大时,电源效率会提高,但电源正常工作最小输入电压也会升高,电路的工作范围变窄;而当电源初次级匝数比减小时,电源正常工作最小输入电压降低,电路的工作范围变宽,但效率会降低。图3给出了不同匝数比时漏极上的电压波形:

其中图3(a)是变压器初次级匝数比为8:7:7,初次级电感量比为110:95,:95的波形,此时的电路输出效率为75%,最小输入电压为14 V;

图3(b)是变压器匝数比为10:7:7,初次级电感量比为180μ:95μ:95μ时的电压波形,此时的电路输出效率为78%,最小输入电压为16 V

图3(c)是变压器匝数比为13:7:7,初次级电感量比为246μ:95μ:95μ时的电压波形,此时的电路输出效率为81%,最小输入电压为20 V

开关电源以其高效率、小体积等优点已获得了广泛应用。而转换器是开关电源中最重要的组成部分,转换器有5种基本类型:单端正激式、单端反激式、推挽式、半桥式和全桥式转换器。在所有的DC/DC隔离变换器中,正激变换器是低电压大电流功率变换器的首选拓扑结构。由于正激变换器使用无气隙铁心,电感值高,原边和负边峰值电流小,铜损小,所以变压器利用率较高,输出效率也很高;其次,正激变换器中输出电感器和续流二极管的存在,也可以有效衰减纹波电流。为此,本文介绍了一种采用单端正激式结构设计的双路输出(%26#177;6 V,1.5 A)DC/DC变换器的设计过程。

1电路工作原理

本变换器的电路原理框图如图1所示。当直流输入电压经过滤波电路进入辅助电源后,即由辅助电源给控制器供电,然后在控制器作用下,用开关管控制电流的通断以形成高频脉冲电流,再经高频变压器,使其在输人为高(开关管接通)时整流二极管导通,从而使串联电感为充电状态,最后经滤波电路向负载传送能量并输出直流电压;相反,在输入低电平(开关管断开)时,电感为放电状态,电路将通过续流二极管继续向负载释放能量,并输出直流电压。为了保持电压稳定,两路输出电压经取样、隔离反馈电路送到控制器后将使输出脉冲宽度随输出电压的变化而变化,从而稳定输出电压。由于变压器原边绕组通过的是单向脉动电流,为避免磁性饱和,确保励磁磁通在每一个开关周期开始时处于初始值,设计时必须使变压器的铁芯磁性复位。

传统的开关电源普遍采用电压型脉宽调制(PWM)技术,而近年来,电流型PWM技术得到了飞速发展,本设计采用电流型控制器UC1843来实现控制回路。UC1843工作频率可达500 kHz,并它具有大电流推拉式输出,低启动工作电流等特点。电路中在开关管通断瞬间,必须供给栅极较大电流,并对栅源极间电容进行快速充放电,以使开关管高速工作。UC1843的输出级为图腾柱式,输出电流为1 A。它不必增加任何外围电路,就可将其直接接到开关管的栅极,并驱动VMOS管高速工作。UC1843具有精度高、电压稳定、外围电路简单优点。相比电压型PWM,电流型PWM具有更好的电压调整率和负载调整率,系统的稳定性和动态特性也有明显的改善。

3双路输出设计

本设计中的双路输出部分电路如图2所示。

其次。也可将采样比较器R1、R2直接跨接到正负电源的输出端上。本设计的逻辑"地"不是电源的输出地.而是以负电压输出端作为采样比较和基准电压的逻辑"地"电位。这样,采样误差将同时反映出正、负2路输出的电压精度变化,并对正、负2路同样存在有反馈作用,以在很大程度上改进2路输出的调整率。

4变压器设计

开关电源的设计主要分为两部分,一是电路部分的设计。二是磁路部分的设计。开关电源变压器是高频开关电源的核心元件,必须进行合理设计才能达到理想效果。一般情况下,开关电源变压器的选用原则如下:

(1)要有较高的饱和磁通密度BS和较低的剩余磁通密度Br,以减少变压器的匝数和铜损。

(2)在高频率下应有较低的功率损耗;因为变压器高频工作时会发热而造成磁心损耗,从而影响电源输出效率,造成波形畸变等不良后果。

(3)适中的磁导率;不同的相对磁导率适合于不同的工作频率,比如相对磁导率为2000的材料,其适用频率在300 kHz~500 kHz。

(4)较高的居里温度;居里温度是使磁性材料失去磁特性时的温度。居里温度值过低,高温工作时会使磁心的饱和磁通密度严重跌落,从而影响正常工作。

为此,本电路根据工作频率、输出功率、模块体积等要求,选用磁心规格为PC40-P11/7Z-52H的TDK磁性材料。其参数见表1所列。

实际绕制变压器时,先根据计算所得的变压器匝数比,以绕满罐为原则来绕制变压器,再在电路中根据输出效率要求和工作电压范围,来观察开关管漏极上的电压波形,并对变压器匝数进行适当调整。事实上,当电源初次级匝数比增大时,电源效率会提高,但电源正常工作最小输入电压也会升高,电路的工作范围变窄;而当电源初次级匝数比减小时,电源正常工作最小输入电压降低,电路的工作范围变宽,但效率会降低。图3给出了不同匝数比时漏极上的电压波形:

其中图3(a)是变压器初次级匝数比为8:7:7,初次级电感量比为110:95,:95的波形,此时的电路输出效率为75%,最小输入电压为14 V;

图3(b)是变压器匝数比为10:7:7,初次级电感量比为180μ:95μ:95μ时的电压波形,此时的电路输出效率为78%,最小输入电压为16 V

图3(c)是变压器匝数比为13:7:7,初次级电感量比为246μ:95μ:95μ时的电压波形,此时的电路输出效率为81%,最小输入电压为20 V

- AD9958高性能可双路输出的DDS器件(02-16)

- 电磁探伤仪电源系统研究(09-22)

- 一种升压型PFM控制DC/DC转换器(11-11)

- 抑制电子设备中电磁干扰的产生来源(10-04)

- DC/DC模块的电源纹波测量(03-15)

- 一种基于三电平的单级PFC电路设计(12-03)