处理器的高效率电源管理

时间:02-13

来源:EDN

点击:

预测到2010年,处理器将工作在1V和100A电流,到2020年希望处理器的电源电压将是0.7V和更高电流。处理器工作在1V,100A(或更高)和GHz频率时的高效电源管理成为设计人员面对的困难任务。

设计人员可以提供低电压、大电流微处理器电源。但增加高效率(90%或更高)的要求时,采用当今的元件和技术可达到的效率为70%~80%。

VRD配置

VRD(Voltage regulator-down)配置把所有元件直接安装在计算机母板上,为大部分处理器供电。大部分VRD有8位电压识别(VID)码,其8位输入线直接连接到处理器的相应8个VID引脚。在电压稳压器根据感测器的微处理器VID码,设置处理器所需的工作电压。处理器也可以采用动态电压识别来改变时钟频率和工作电压,以响应处理器的工作负载和热响应。

Intel公司VRD11.0处理器电源供电设计指南中,为5个不同处理器给出所用电源设计指南为:

·最高电源电压:1.4V~1.425V;

·最大电流:75A~125 A;

·在所有线路、负载和环境条件下,严格的输出电压调整±5%;

·非常低的纹波,通常小于10mVrmsp-p;

·效率75%~80%;

·快速瞬态响应,与微处理器时钟频率一致;

·过压保护;

·过流(短路)保护;

·过温保护;

·功耗元件的热管理;

·相当小的封装尺寸,使电源可以安置在靠近微处理器负载处。

多相变换器

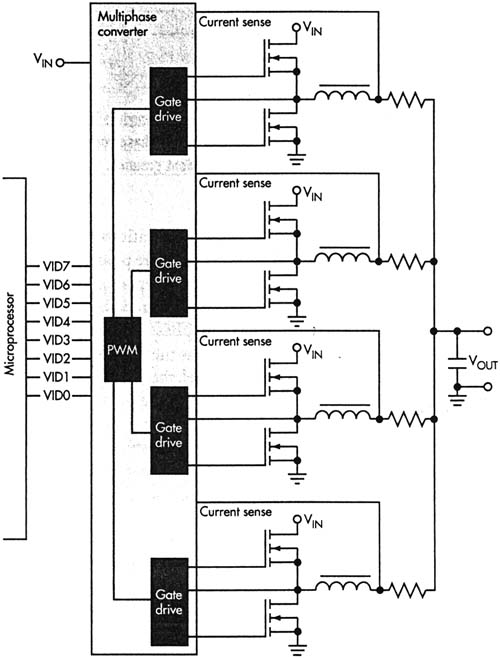

可以满足当今处理器电源要求的唯一拓扑是多相开关模式变换器。这种变换器采用两个或更多相同、组合单元,把这些单元输出连接起来,其输出是所有单元输出的总和(图1)。

设计人员可以提供低电压、大电流微处理器电源。但增加高效率(90%或更高)的要求时,采用当今的元件和技术可达到的效率为70%~80%。

VRD配置

VRD(Voltage regulator-down)配置把所有元件直接安装在计算机母板上,为大部分处理器供电。大部分VRD有8位电压识别(VID)码,其8位输入线直接连接到处理器的相应8个VID引脚。在电压稳压器根据感测器的微处理器VID码,设置处理器所需的工作电压。处理器也可以采用动态电压识别来改变时钟频率和工作电压,以响应处理器的工作负载和热响应。

Intel公司VRD11.0处理器电源供电设计指南中,为5个不同处理器给出所用电源设计指南为:

·最高电源电压:1.4V~1.425V;

·最大电流:75A~125 A;

·在所有线路、负载和环境条件下,严格的输出电压调整±5%;

·非常低的纹波,通常小于10mVrmsp-p;

·效率75%~80%;

·快速瞬态响应,与微处理器时钟频率一致;

·过压保护;

·过流(短路)保护;

·过温保护;

·功耗元件的热管理;

·相当小的封装尺寸,使电源可以安置在靠近微处理器负载处。

多相变换器

可以满足当今处理器电源要求的唯一拓扑是多相开关模式变换器。这种变换器采用两个或更多相同、组合单元,把这些单元输出连接起来,其输出是所有单元输出的总和(图1)。

|

图1 四相电压稳压器用分离的栅极驱动器、分立的功率MOSFETs和1个分离的PWM控制器,与微处理器连接靠8位VID码 为了理解多相变换器的优点,首先看看单相变换器提供大电流和低电压时的缺点。用一般单相变换器,其输出汶波和动态响应的改善是靠提高工作频率。 另外,在较高频率时,输出电感器和输出电容器的物理尺寸和数值变小。在频率达到一定限值后,变换器开关损耗增大,效率下降。这迫使在工作频率和效率方面做设计折衷。 为了克服这些单相频率限制,多相单元工作在一个共同的频率,但移相结果是变换开关发生在由共同控制芯片控制的规则间隔内。控制芯片交错排列每个变换器的开关时间,所以,每个变换器开关之间的相位角是360?/n(n是变换器单元数)。因为单元输出是并联的,所以,有效的输出纹波频率是nxf(f是每个单元的工作频率)。这种方法具有较好的动态性能和显著小的去耦电容(与单相系统相比)。 单元的电流均分是必须的。因此,一个单元不能"霸占"大多数电流。理想情况是每个多相单元应该消耗相同量的电流。为了实现相等电流均分,必须监视和控制每个单元的输出电流。 多相变换器有几个重要的优点:每个单元提供总输出功率的1/n,这使得每个相所用的电感器的尺寸数值变小;热耗分布优点,因为每个单元中的功率半导体只需要处理总功率的1/n,这降低了任何热点温度、增加了可靠性,并允许有较高的总功率性能。 另外,等效频率增高不会招致进一步的开关损耗,这可以采用较小的等效电感,从而缩短负载瞬态周期时间。输出电容器中降低的纹波电流使输出纹波电压变低,这可采用更小或更便宜的输出电容器。 在选择相数时,应考虑多相变换器的一些缺点。缺点1,需要较多的开关和输出电感器,这会导致较高的系统成本;缺点2,需要更复杂的控制,这是因为有多个变换器单元,相互之间不均匀电流均分的可能性是可能的;缺点3,增加了电路布线的复杂性。 随着工作电流要求的增高,需要有更多的单元相。一个最佳的设计需要折衷考虑相数、每个相的电流、开关频率、成本、尺寸的效率。更高的输出电流和更低的电压,需要更严格的输出电压调整。多相设计可采用几种实用的方法。 一种方法是采用带集成MOSFET驱动器的PWM(脉宽调制)控制器IC。然而,片上栅极驱动器产生的热和噪声会影响控制器性能。级连这类芯片以增加更多相是不现实的。用这种配置实现精确的电流均分是困难的。这种方法3相是限制相数。 另一种方法是采用分离的控制器和分离的栅极驱动器,使PWM控制器与栅极驱动器的热和噪声隔离。然而,电流均分会更复杂,因为电流感测信号路由到控制器。还有另外的控制器-驱动器延迟,这是因为它们是分离的IC。 另一种方法是采用一个带集成栅极驱动器和内置同步和电流均分的控制器。这种方法只允许偶数相数。它简化了设计,但可导致未用或多余硅片、引脚和外部元件。最重要的是片上所产生的驱动器热和噪声可能会降低控制器性能。 所以,现有的方法在选择相数中不能提供所需的自由度。理想的方法是一种可伸缩的拓扑,它能容易地增加或去除任意多相单元,而且不影响性能。这种方法必须能够在分布的相单元中相等地均分电流。这样的技术使寄生效应最小,并容易板布线。 |

- 选择最佳的电压基准源(11-29)

- 对电压参考进行滤波以获得低噪声性能(01-16)

- 可编程快速充电管理芯片MAX712/ MAX713及其应用(01-23)

- 改进型全桥移相ZVS-PWMDC/DC变换器(01-23)

- 负输出罗氏变换器实用性剖析(01-09)

- 通信电源设备对杂音电压的控制要求(02-13)