一种新型低功耗两级运算放大器的实现

|

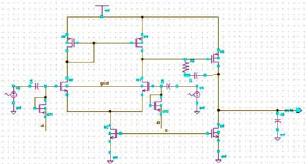

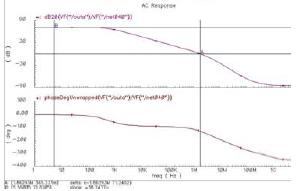

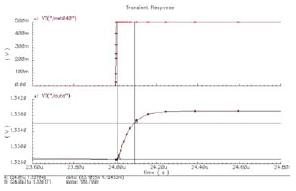

图4 基于准浮栅技术的两级运算放大器 输入信号通过输入耦合电容C 耦合到输入管的栅极。将两个输入的NMOS 管的栅极偏置到VDD 上,因而两个输入管处于常导通的状态,从而降低了对输入信号的要求,即使输入很低电压,因为两个输入管的常导通状态,电路也能正常工作,从而也降低了对电源电压的要求,随着电源电压的下降,偏置电流也随之降低,使电路能够实现低功耗的要求。 采用准浮栅技术对电路进行改进后,由于该运放的输入为交流耦合电路,因此可以滤掉由输入电压所带来的直流失调。但是也从而也带来了一个缺点,准浮栅运放只对交流信号进行放大,而不能作为直流比较器。且由于在输入管引入了一个二级管连接的工作在截止区的MOS 管大电阻,因此可以判断出主极点位于输入管处,这样的一个大电阻会引起单位增益带宽的减小,但是它也会带来更大的相位裕度,使系统更稳定。我们在选择管子参数的时候,要考虑到它的具体应用环境,来决定它的性能指标。 准浮栅技术主要是实现低功耗问题,因此在设计中,运放的静态功耗是一个非常重要的指标,在两级运算放大器设计中,该电路的静态功耗为

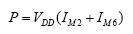

其中IM2为一级运放的偏置电流,IM6为二级运放的电流。可以看出为了减小运放的功耗,偏置电流应尽可能的小,但是随着电流的减小又会带来运放转换速率的减小,这需要根据设计要求进行一个折中的考虑。 表1 传统放大器与改进以后的放大器性能的比较

|

- RS-485网络设计降低功耗问题(01-26)

- 低功耗CMOS电压基准源的设计(08-27)

- 创建理想的低功耗设计(01-14)

- 新一代电池供电装置的超低功耗设计(07-18)

- 基于绝热逻辑的低功耗乘法器电路设计(07-23)

- 低功耗ADC实现“绿色”采集(01-28)