多路信号采集器的硬件电路设计

时间:10-21

来源:EDN

点击:

|

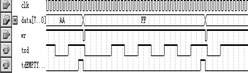

图3 发送模块时序图 3.4接收程序设计 接收电路比发送电路要复杂,接收电路要实时检测起始位的到来,一旦检测到起始位到,就要将这一帧数据接收下来。接受电路一共设计有三个并行进程如图4所示,其中 进程1 负责产生9600bps波特率,使系统能够在9600的波特率与外界系统通讯。进程2 产生接收信号RXD的完成标志位,每次在接收到帧的起始位时,标志位RXDF变高,在完成接受数据后,标志位RXDF变低。进程3负责将RXD信号输入的10位串行数据,依照10位的帧格式,先去掉串口的接收起始位和接收结束位,取其中的8位有效数据,并将8位有效数据进行串并转换,变成并行数据后,由8位数据总线DATA0~DATA7并行输出。

|

- 基于USB接口的便携式信号采集器 (03-15)

- 基于DM642的视音频采集器的设计(09-01)

- 基于CPLD的多路信号采集器的硬件电路设计(12-22)

- 数据采集硬件:如何避免缺陷与误差(07-01)

- 基于Nios II的数字音频录放系统的设计(01-08)

- 锂离子电池智能充电器硬件的设计(01-16)