多路信号采集器的硬件电路设计

时间:10-21

来源:EDN

点击:

1引言

存储测试的特点是集多参数微型传感器及信号调整、信息采集、信息存储及传输接口电路为一体,对被测物体的工作环境、运动控制等多通道、大容量参数进行(实时、动态)数据采集、存储、事后回收、数据再现、数据分析。目前,存储测试技术已经在许多重大武器型号的研制、生产中得到成功应用,并取得了一系列重要科研成果。解决了过去无法解决的重大测试难题,显示出了突出的优越性。

2 硬件设计

2.1 系统框图:

本系统中有1路速变模拟信号、8路缓变模拟信号、4路数字信号。该采集系统能实现采集0~10V之间的模拟信号,其中单路速变模拟信号采样率不低于40Khz,8路缓变模拟信号采样率不低于12.5Khz,两者精度均在0.1%,同时还能够存储4路数字信号。信号记录时间均不低于0.75s,整体设计如图1所示。

存储测试的特点是集多参数微型传感器及信号调整、信息采集、信息存储及传输接口电路为一体,对被测物体的工作环境、运动控制等多通道、大容量参数进行(实时、动态)数据采集、存储、事后回收、数据再现、数据分析。目前,存储测试技术已经在许多重大武器型号的研制、生产中得到成功应用,并取得了一系列重要科研成果。解决了过去无法解决的重大测试难题,显示出了突出的优越性。

2 硬件设计

2.1 系统框图:

本系统中有1路速变模拟信号、8路缓变模拟信号、4路数字信号。该采集系统能实现采集0~10V之间的模拟信号,其中单路速变模拟信号采样率不低于40Khz,8路缓变模拟信号采样率不低于12.5Khz,两者精度均在0.1%,同时还能够存储4路数字信号。信号记录时间均不低于0.75s,整体设计如图1所示。

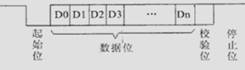

| 图1 采集系统整体框图 2.2信号调理设计 在本系统中,由于模拟输入信号的电压范围是0~10V,所以此次设计使用LM324运算放大器组成的比例电路将输入信号变换成0~2.5V电压。然后输入模拟开关经过跟随器后,再输入A/D转换器。4路数字信号使用一个5V的稳压管,将输入数字信号中大于5V的高电平信号钳制在5V,起到了调压的作用。如果是低于5V,那么电压将不改变。 2.3输入通道设计 存储测试系统常常需要多通道同时采集。此次设计中根据被测信号的特点选用ADG506模拟开关进行各通道的切换,该模拟开关具有开关速度快、泄漏小等特点,从而用最简单的硬件电路完成多路信号的存储测试。 2.4采集芯片选用: 此次设计采用AD公司的AD7492采集芯片,AD7492为12位高速、低功耗、逐次逼近式AD转换器。它可在2.7V-5.25V的供电电压下工作,采样频率最高为1.25MSPS,从而为正确采集回速变、缓变信号提供保障。 2.5存储电路设计 此系统中,我们共有1路速变模拟信号,8路缓变模拟信号,4路数字信号。首先,对于单路速变信号而言,其最低采样频率为40kHz,系统要求的最低记录时间为0.75S此次设计中,用了一个模拟开关和一个AD7492循环进行数据采集,将1路速变信号和8路缓变信号交叉安排在ADG506上,这样在每次速变信号采集后,紧接着采集8路缓变信号,经过循环交叉采集后,便使得速变信号采样率是缓变信号采样率的8倍,所以速变信号采样率为8×12.5kHz≥40kHz。其次,对于8路缓变信号,其单路采样率为12.5kHz, 记录时间为0.75s,共8路。最后,存储4路数字信号。由于我们采用12路的AD采集,所以4路数字信号与AD产生的高4位信号合起来组成8位一起存入512K的SRAM 628512。因此不再单独占用空间。由以上分析我们可以得到存储容量为:M≥12.5kHz×8路×2×0.75+12.5kHz×8次×2×0.75=300kbyte。为了方便读数和数据分析,在每组数据前加上通道标志位,以区分是哪一路信号。为了确保存储空间,此次设计我们一共选用两块容量为512K的SRAM进行数据存储。AD转换和CPLD处理后的采集信号通过74LVC4245电平转换后送入SRAM进行存储。 3 CPLD实现计算机异步串行通讯设计 3.1异步串行通信的帧格式 在异步串行通信中,数据位是以字符为传送单位,数据位的前、后要有起始位、停止位,另外可以在停止位的前面加上一个比特位(bit)的校验位。其帧格式仍然采用1位开始位+8位数据位+1位停止位.如图2所示。此次设计中没有奇偶效验位。停止位,为逻辑1,总在每一帧的末尾。此次设计中停止位为1位。

|

- 基于USB接口的便携式信号采集器 (03-15)

- 基于DM642的视音频采集器的设计(09-01)

- 基于CPLD的多路信号采集器的硬件电路设计(12-22)

- 数据采集硬件:如何避免缺陷与误差(07-01)

- 基于Nios II的数字音频录放系统的设计(01-08)

- 锂离子电池智能充电器硬件的设计(01-16)