低功耗CMOS电压基准源的设计

时间:08-27

来源:现代电子技术

点击:

be电压叠加,产生与温度无关的基准电压,电容C2是为了滤波,降低噪声。

将式(7)代入(6)可以看出,只要合理设置晶体管的宽长比和电阻R2,R1的比值就可以得到与温度无关的基准电压。

由于电压基准源电路存在2个电路平衡点,零点和正常工作点。当基准源工作在零点时,晶体管M8,M9栅源电压为高,M10,M11管栅源电压为低,PTAT电路没有电流产生,启动电路就是避免电压基准工作在零点上。本文提出的启动电路的最大特点是不耗电,它由晶体管M1~M5以及电容C1组成。当电源电压为低时,若电容C1上存有电荷,则M3导通,将电荷放完,等电源电压为高时,M1,M2导通,流过M2的瞬间大电流迅速将M5打开,同时将M8,M9的栅电位拉低导通,产生PTAT电流,电路正常工作,当M12,M13栅压升高时,M4导通,将M5栅压拉低,启动电路停止工作,几乎不消耗电流,达到了低功耗的目的。启动时间由M2管子的大小和电容C1决定。电压基准的启动电路仿真结果如图3所示,启动时间只要50μs,启动之后只要消耗82 pA的电流。若没有M3,电容C1上可能存在电荷没有放完,再次启动时有启动不了的可能。

本文介绍的电压基准源采用CSMC 0.5 μm,两层POLY,一层金属的CMOS工艺实现,已经成功流片。该工艺的阈值电压分别为N管0.87 V,P管-0.97 V。由于产生PTAT电流的2个P型管存在失调会导致2支路不平衡,版图匹配技术可以减少失调,在版图中可以增加虚拟晶体管使匹配晶体管间的环境相同来减少失调,同时,晶体管M7要在一个独立的N阱中,使与M6的偏置条件一样来减少失调。二极管可以用CMOS工艺中寄生的PNP三极管实现,N阱中的P+区作为发射区,N阱本身作为基区,P型称底作为集电区,电阻采用具有负温度系数的高阻POLY2电阻,方块阻值为2 kΩ/□,节省面积。电压基准的版图如图4所示,版图面积为:490μm×75μm-0.036 75 mm2。

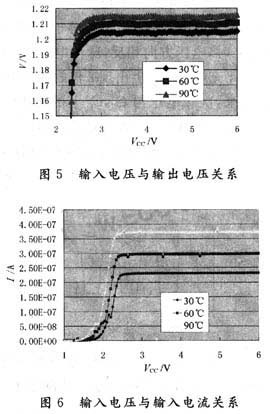

图6是不同温度下电压基准电路消耗电流与电源电压的关系。电压基准电路在正常工作时消耗电流与电源电压无关,与温度成比例。在20~100℃之间,室温下工作时消耗电流小于250 nA,100℃时工作电流不超过380 nA,与仿真结果吻合。在6 V工作电压下,最大功耗不超过2.28μW。

6 结 语

本文利用工作在弱反型区的晶体管特性设计一款最大消耗电流不超过380 nA的电压基准电路,功耗低,面积小。测试结果表明,电源电压由2.5~6 V变化时,线性调整率平均为0.025%,温度在20~100℃之间变化时,测得的平均温度系数是64 ppm/℃。但是该电压基准电路由于采用了共源共栅结构,最小工作电压2.5 V有点偏高,采用低压共源共栅结构将会获得更优的性能。

- RS-485网络设计降低功耗问题(01-26)

- 一种新型低功耗两级运算放大器的实现(01-20)

- 创建理想的低功耗设计(01-14)

- 新一代电池供电装置的超低功耗设计(07-18)

- 基于绝热逻辑的低功耗乘法器电路设计(07-23)

- 低功耗ADC实现“绿色”采集(01-28)