毫瓦级功率实现千兆赫兹信号驱动的模拟解决方案

ADC14DS105KARB接收器参考设计板

ADC14DS105KARB是一个近零中频接收器参考设计板,它所使用的组件如下:两个LMH6552 1.5GHz 带宽差分电流反馈放大器;ADC14DS105 带有LVDS输出的14位、1GHz、双路、105MSPS模/数转换器;LMK02000低抖动精密时钟调整器,它带有一个可在100Hz到20MHz带宽范围内提供128fs抖动的集成锁相环路(PLL);数个高能源效率的电源管理电路。

ADC14DS105KARB (其框图见图2)是一块中频接收器子系统参考设计板,它采用一对LMH6552差分驱动器和一个双路ADC,可以立即测试适用于直流电至40MHz信号频率的正交直接转换或近零中频接收器。这个接收器架构现已被广泛应用到WiMAX 和WCDMA接收器系统。

图2. 参考设计板的框图。

由于ADC的输入带宽高达1GHz,而差分放大器增益级的带宽高达1.5GHz,因此若输入信号不超过40MHz,大信号的信噪比可达 73.3满刻度分贝值(dBFS),而无杂散信号动态范围(SFDR)则超过85dBFS。这款电路板除了采用LMH6552之外,还安装了美国国家半导体的14位、 105MSPS、低失真、低噪声、并可输出串行LVDS数据的双通道模拟/数字转换器ADC14DS105、低抖动时钟调整器LMK02000以及多颗高能效的电源管理IC。

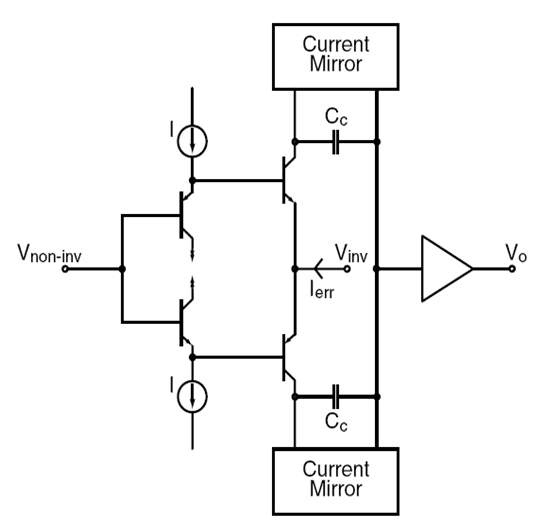

LMH6552是一个高性能全差分放大器,它能提供驱动14位高速数据采集系统所需的超强信号保真度和宽阔的大信号带宽。通过采用获得专利的差分电流模式输入级架构,LMH6552能够在不牺牲响应平坦度、带宽、谐波失真或输出噪声性能下,在增益大于一个单位级下工作。

配合外置的增益设置电阻器和集成式的共模反馈, LMH6552可被配置成一个差分输入到差分输出,或信号单端输入到差分输出的增益级。LMH6552的输入端可作交流耦合或直流耦合,因此可以应用到诸如通信系统及高速示波器的前端电路等非常广泛的领域。

LMH6552的电流反馈拓扑使器件即使在高增益下,只需选择合适的反馈电阻(RF1, RF2),便可提供有超强增益平坦度和噪声性能的增益和带宽独立性。在大多数的应用中,RF1都被设置成等于RF2,因此增益是由RF/RG的比例来决定。

LMH6512的数据表根据各种各样的增益给出最优的反馈电阻器数值。无论是过大或过小的RF都会对稳定性构成影响。在许可的情况下,反馈电阻器还可以调整频率响应。

电流反馈放大器的另一优点是需要内部增益级相对较低。通常一个电流反馈放大器主要包含有一个输入缓冲器、一个增益级和一个输出缓冲器。拥有较少的增益级意味着经过开环电路的延迟会较少,从而在相同的功耗下能获得较大的带宽。

图3. 基本的电流反馈(CFB)拓扑。

图3中的基本电流反馈(CFB)拓扑是一个单级放大器。电路中的唯一高阻抗节点是在输出缓冲器的输入。VFB放大器通常需要两个或以上的增益级才能获得足够的开环增益,这些附加的增益级不单会增加延迟,而且还会降低带宽的稳定性。

图4. LMH6552电路和5阶低通滤波器。

图4说明了放大器的参考电路板配置。当中的输入是50Ω和直流耦合。LMH6552被配置成单端到差分模式转换,而ADC14DS105的VCOM输出会用作放大器的共模输入。每一个放大器都被配置成有6分贝的增益,因此最大的输入信号电平为1Vp-p,并在放大器的输出处产生出2Vp-p。这里建议放大器最好由一个双电源轨来供电(+/- 5VDC)。在VCCAA- 和VCCAB-处设置跳线,电路板就可在单电源模式下工作,详细信息可参考LMH6552数据表中有关LMH6552单电源工作的部分。要获得最佳的失真性能(最佳SFDR),建议采用一个低噪声信号发生器来驱动评估板的信号输入,而信号发生器的输出应该经过带通滤波以抑制由信号发生器引入的谐波失真,以及容许进行精确的噪声和失真性能测量。然而,跟随在LMH6552之后的43MHz的5阶低通滤波器可过滤信号发生器的宽带噪声,从而进一步改善ADC的噪声性能。滤波器输出会被模/数转换器采样。

ADC14DS105是世上第一款带有串行化LVDS输出的14位高速、1GHz FPBW的双路模/数转换器,它采用串行化LVDS输出大幅地减少了需要跨过电路板或在电路板之间的导线数量,因此大大地简化电路板的布局。

用来替模拟输入采样的ADC时钟信号是由一个经LMK02000精密时钟调整器控制的VCOX所产生。该LMK02000为用户提供一个设有时钟分配区的超低噪声锁相环路(PLL),它可提供5个LVPECL输出和3个LVDS输出(全为差分)。

每一条在LMK02000上的时钟输出通道均包含有一个分频器模块和延迟调整时钟。LMK02000一般都会跟一个低抖动的VCOX连接在一起。在这种情况下,一个Crystek 型号的CVHD-950X-100.0可提供一个单端CMOS时钟信号来驱动ADC的时钟输入。LMK02000 的锁相环路可把这个VCOX锁定到一个25MHz的参考振荡器(Connor-Winfield 型号CWX823),而LMK02000的锁相环路计数器、相位检测器和电荷泵是采用PIC微控制器电路板来编程的,详情请参看用户指南。

LMK02000的RMS信号抖动仅为128fs(输入的时钟范围由100Hz到20MHz)。图5表示出时钟的相位噪声性能,该性能值是在LMK02000的CLKout4情况下测量出的。从VCOX产生出来的单端时钟信号会供给ADC14DS105的CLK输入。

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)