功率分配系统(PDS)设计:利用旁路电容/去耦电容

时间:04-29

来源:Eefocus

点击:

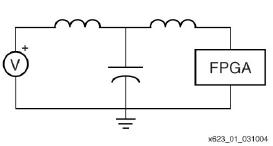

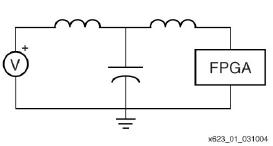

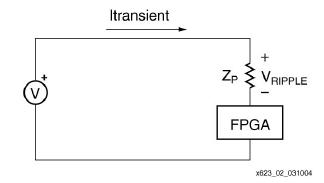

图1:简化的PDS电路图 图2是一个更加简化的PDS电路图,显示了分解为频率相关电阻的所有电抗元件。

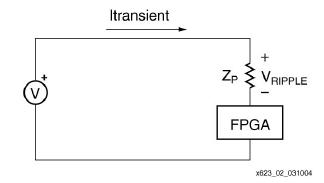

图2:更加简化的PDS电路图

电感的作用是什么?

电容和PCB电流通道的属性之一就是延迟电流变化。因此,电容不能立即响应瞬态电流,或者高于其有效频率范围的变化。这种属性称为电感。

可以将电感视作电荷的动量。其中,电荷在导体中以一定速率移动,代表一定量的电流。如果电流水平发生变化,那么,电荷就必须以不同的速率移动。由于该电荷有一定的动量(保存的磁场能量),因此,要在一段时间后电荷才能实现减速或加速。电感越强,对改变的阻力就越强,从而使得电流需要更长时间才能发生变化。

PDS的目的是满足器件可能有的任何电流需求,并尽可能迅速地响应这种电流需求的变化。如果未能满足这种电流需求,那么,器件的电源电压就会发生变化。这就是电源噪声。由于电感会阻碍旁路电容迅速响应变化的电流需求的能力,所以应当最大限度地降低电感。

图1显示了FPGA和电容之间的电感和电容和稳压器之间的电感。这种电感是电容自身以及PCB中的所有电流通道的寄生现象。必须最大限度地降低所有这些电感。

电容寄生电感

在电容的各种属性中,通常认为电容值是最重要的。然而,在PCB PDS设计领域,寄生电感属性(ESL,即等效串联电感)与电容值同样重要,甚或更为重要。

影响寄生电感的一个重要因素是封装的尺寸。一般而言,极为简单、体积小巧的电容的寄生电感低于体积较大的电容。就像较短的电线产生的电感低于较长的电线,较短的电容产生的电感也低于较长的电容。同样地,就像较粗或较宽的电线产生的电感低于较细的电线,较粗的电容产生的电感也低于较细的电容。

由于这些原因,在选择去耦电容时,应当选择特定额定值中体积最小的封装。类似地,对于特定封装尺寸(尤其是固定的电感值),应当选择采用该封装的电容中电容值最高的。

表面安装式芯片电容是目前市场中体积最小的电容,因此,是分立式旁路电容的理想选择。对于低于2.2 μF的极小的电容值,如0.001 μF,通常使用X7R或X5R型电容。这些电容具备很低的寄生电感和可接受的温度特性。对于较高的电容值,如1000 μF,则使用钽电容。这种电容具备较低的寄生电感和相对较高的等效串联电阻(ESR),使其具备较低的品质因素,从而能够提供范围广泛的有效频率。钽电容不仅具备相当高的电容值,而且封装尺寸也不大,从而降低了板上空间占用。如果没有钽电容可用,可以使用低电感电解电容。具备类似特性的其他新技术也可使用。

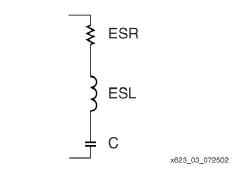

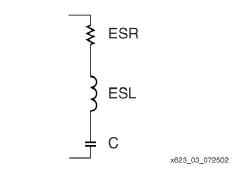

真正的电容具备多种特性,包括电容值、电感以及电阻。图3显示了一个真正的电容的寄生模式。应当将一个真正的电容视作一个RLC电路。

|

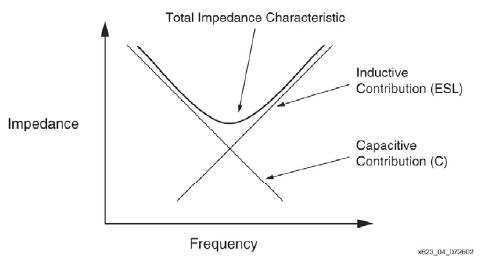

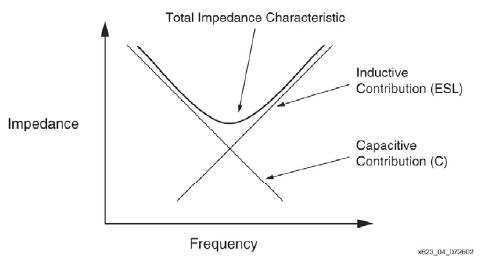

图3:真正的、而不是理想的电容的寄生现象 图4显示了一个真正的电容的阻抗特性。在这张图中的重合的两条曲线对应于电容的电容值和寄生电感(ESL)。这两条曲线共同构成了因电容的寄生效应而产生的该RLC电路的总阻抗特性。

| | 图4:寄生效应对总阻抗特性的贡献 | 随着电容值的增加,电容曲线将逐渐下降,并向左移动。随着寄生电感的降低,电感曲线也将逐渐下降,并向右移动。由于采用特定封装的各种电容的寄生电感基本上是固定的,该电感曲线也保持固定。如果选择了采用该封装的不同电容值的电容,其电容曲线将相对于该固定的电感曲线向上或向下移动。降低采用特定封装的电容的总阻抗的唯一方法就是降低其电容值。使寄生电感曲线向下移动(从而降低总阻抗特性)的唯一方法,就是并联多个电容。

| | |