什么是并行比较型ADC(模数转换器)

时间:01-24

来源:

点击:

| 9VREF/15≤v1<11VREF/15 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 11VREF/15≤v1<13VREF/15 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

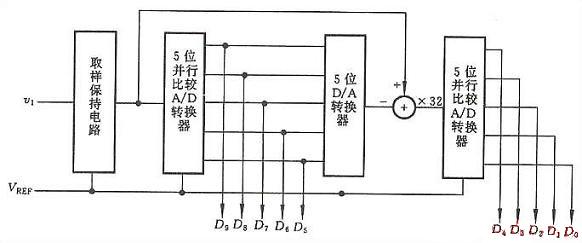

| 13VREF≤v1< VREF | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 4.特点 图11.9.2 分级并行转换10位A/D转换器 |

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)