用LTB技术改善多相直流转换器的响应速度

时间:01-10

来源:电子工程专辑

点击:

高性能微处理器需要具有快速瞬态响应的低压大电流供电系统。因此,交织多相同步降压转换器作为这些微处理器的电压整流模块(VRM)获得广泛应用,因为它们允许在小信号条件下采用更快速的系统控制器,可以减少输出电压纹波、降低输入/输出电容的成本。不过,在具有很大和快速的负载变化期间,交织相移会影响输出电压。

在与输出功率相关的交流变量基础上对系统稳定性和小信号行为的研究结果表明:系统的状态变量是流经等效电感的总电流和输出电容上的电压降。多相交织系统可以用这些变量完全表征,并等效于只有一个单相位的DC/DC转换器,其中,线圈可以被并联的全部电感(等效电感)代替,等效开关频率是单相开关频率的N倍(N是相位的数量)。

由这种模型可以看出,为什么用比单相系统更高的误差放大器斜率(GBWP)可以实现更快的控制系统。当然,这样做还有助于保持输出电压的稳定,即使在负载瞬变时也能很好地得到稳压。然而,最近的CPU电气规范中负载瞬变速率已经高达1200A/us(50ns为100A),使得控制系统几乎不可能及时响应这种陡峭的变化。结果是中频以上输出滤波器电容的成本上升,例如22uF多层陶瓷电容(MLCC)。

动作延时

目前使用的控制器一般要么是上升沿架构要么是下降沿架构,每种架构都有各自的优缺点。采用下降沿控制架构的控制器在每个时钟周期的开始打开,这种控制器可以响应控制器打开时发生的任何瞬态事件。然而,如果瞬态事件发生在控制器关闭期间,那么它必须等到下一个时钟周期才能做出响应。而采用上升沿架构的控制器在每个时钟周期内是关闭的,这种控制器可以响应在它关闭时发生的瞬态事件,但必须等到下一个时钟周期才能响应这种控制器打开时发生的瞬态事件。在这两种架构中,一般都会在PWM比较器的输出端放置一个锁存器,用以在响应瞬态事件时建立一个周期的延迟。

双沿调制器在判断何时打开或关闭时不受时钟周期的约束,打开信号取决于误差信号。同样地,误差信号会通知控制器何时关闭。这种架构再加上快速输出反馈即可允许所有相位同时响应瞬态事件。虽然基本的双沿调制器可以改善系统性能,但很重要的是还能解决引入系统响应延迟和妨碍理想瞬时响应的其它架构问题。如果将"动作延时(action delay)"看作是从控制器识别负载瞬变的发生到命令接通所有上边(highside)功率MOSFET的时间,那么对这一延时的影响因素至少有以下几种:

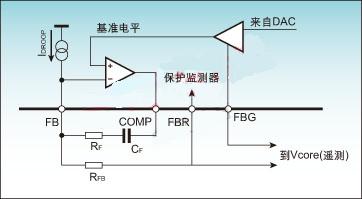

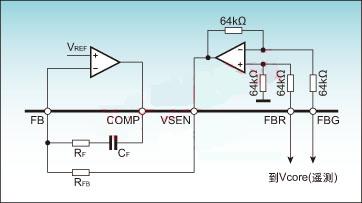

1. 遥测(Remote sense)用来以完全差分的方式检测CPU上的电压,采用运放实现。运放引入的延时Trb=1/GBWPrb(Trb=100ns),其中GBWPrb在10MHz左右。遥测放大器必须从反馈路径中移除,这可以通过只检测远端内核地(core ground)实现,这样会损失高频共模抑制比(CMRR)。图1是传统的远端缓存连接,这里的远端缓存会引入延时Trb,因为它位于反馈路径上。图2所示的遥测是在反馈路径外实现的,因此Trb=0。

在与输出功率相关的交流变量基础上对系统稳定性和小信号行为的研究结果表明:系统的状态变量是流经等效电感的总电流和输出电容上的电压降。多相交织系统可以用这些变量完全表征,并等效于只有一个单相位的DC/DC转换器,其中,线圈可以被并联的全部电感(等效电感)代替,等效开关频率是单相开关频率的N倍(N是相位的数量)。

由这种模型可以看出,为什么用比单相系统更高的误差放大器斜率(GBWP)可以实现更快的控制系统。当然,这样做还有助于保持输出电压的稳定,即使在负载瞬变时也能很好地得到稳压。然而,最近的CPU电气规范中负载瞬变速率已经高达1200A/us(50ns为100A),使得控制系统几乎不可能及时响应这种陡峭的变化。结果是中频以上输出滤波器电容的成本上升,例如22uF多层陶瓷电容(MLCC)。

动作延时

目前使用的控制器一般要么是上升沿架构要么是下降沿架构,每种架构都有各自的优缺点。采用下降沿控制架构的控制器在每个时钟周期的开始打开,这种控制器可以响应控制器打开时发生的任何瞬态事件。然而,如果瞬态事件发生在控制器关闭期间,那么它必须等到下一个时钟周期才能做出响应。而采用上升沿架构的控制器在每个时钟周期内是关闭的,这种控制器可以响应在它关闭时发生的瞬态事件,但必须等到下一个时钟周期才能响应这种控制器打开时发生的瞬态事件。在这两种架构中,一般都会在PWM比较器的输出端放置一个锁存器,用以在响应瞬态事件时建立一个周期的延迟。

双沿调制器在判断何时打开或关闭时不受时钟周期的约束,打开信号取决于误差信号。同样地,误差信号会通知控制器何时关闭。这种架构再加上快速输出反馈即可允许所有相位同时响应瞬态事件。虽然基本的双沿调制器可以改善系统性能,但很重要的是还能解决引入系统响应延迟和妨碍理想瞬时响应的其它架构问题。如果将"动作延时(action delay)"看作是从控制器识别负载瞬变的发生到命令接通所有上边(highside)功率MOSFET的时间,那么对这一延时的影响因素至少有以下几种:

1. 遥测(Remote sense)用来以完全差分的方式检测CPU上的电压,采用运放实现。运放引入的延时Trb=1/GBWPrb(Trb=100ns),其中GBWPrb在10MHz左右。遥测放大器必须从反馈路径中移除,这可以通过只检测远端内核地(core ground)实现,这样会损失高频共模抑制比(CMRR)。图1是传统的远端缓存连接,这里的远端缓存会引入延时Trb,因为它位于反馈路径上。图2所示的遥测是在反馈路径外实现的,因此Trb=0。

图1:全差分CPU遥测,采用传统远端缓存连接

|

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 具有过压保护的低压5A/12V直流电源(11-20)