功率芯片结合纳米技术推进功率转换技术进步

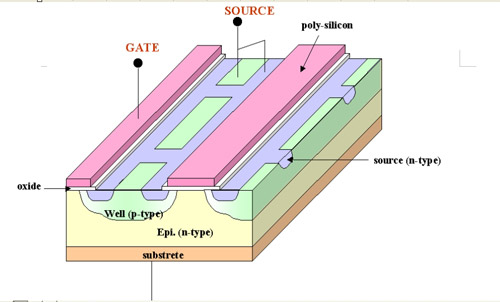

图3. 升压二极管器件的剖面图 控制器架构 控制器由主变压器(T)供电(Vcc引脚),即辅助次级绕组变压器(图中未标明)产生一个相对较低的电压(15V)。由于每个控制器I/O引脚的电压都低于15V,因此该芯片采用低压密集型BiCMOS工艺。当PFC和PWM两部分的运作协调有效时,可以最低的成本(BOM)实现PFC和PWM功能。PFC部分通过上升沿调节控制。MOSFET Q1在时钟边缘关断,并根据PFC方波的前导/上升沿,在环路控制下导通。PWM用"拖尾"调制进行控制。MOSFET Q2在时钟边缘导通,并根据PWM方波的拖尾/下降沿,在环路控制下关闭。相应地,在同步时钟的作用下,两个晶体管决不同时消耗电流,这样进一步重新分散电流,从而使高电压输入电容的数值降至最小。请注意,在50Hz时,波型与图1中的曲线类似,当时钟频率为67KHz时,开关调节器的限幅波形使电流出现纹波。 离线功率晶体管 线路与变压器基层之间的所有二极管及DMOS开关均为高压器件。IEC 61000-3-2规定单相供电线路中的电压最大不超过240VRMS(三相线路最大为415VRMS)。因此,这些元件可承受400V至1000V电压。图3的升压二极管的反向电压高(600V),正向压降小(8A时为1.5V),它是超快速的恢复整流器(trr<60ns)。它的玻璃钝化离子注入外延结构如图3所示。其它高压元件为可承受600V电压的超快速ΜF4005续流二极管和开关Q1-3。它们都是采用平面条纹DMOS工艺制造的500V N沟道增强型MOSFET,开关速度高,开态电阻非常低(在10V VGS下的开态电阻为0.73()。 转换为低电压的DC-DC转换 总线电压VBΜS (如12V)通过开关调节器(一般为同步降压转换器)分配和降低,将电压降低为常用的3.3V、2.5V、1.8V或VCPΜ。达到50A负载的理想上升沿波谷控制结构是两相交替同步降压转换器,每相的开关频率可达1MHz。该IC可直接驱动分立DMOS晶体管的高边和低边,其集成驱动器的阻抗低(1欧)。

|