功率芯片结合纳米技术推进功率转换技术进步

时间:01-09

来源:国际电子商情

点击:

系统级芯片(SOC)公司纷纷预测: 在未来的几年里,完整的信号回路(数字+模拟+存储器), 甚至GSM系统(包括电源管理)将集成于一体。纳米级光刻技术(最小尺寸小于100nm)的发展推动了集成技术的进步,事实上存在产品自身的技术限制。然而,在一个芯片上集成的晶体管越多,它们的工作电压则越低,例如,0.13μm级芯片的工作电压仅为1-2V。

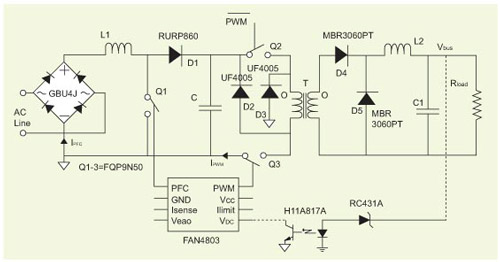

另一方面,功率芯片制造商正不断开发能够处理高电压和大电流的技术。将交流电网电压转换至中间母线需可靠的设备提供数百伏电压和数安培电流。同时,再由母线电压转换至最终负载电压则需要数百安培电流的低压设备。上述功率转换已在个人电脑上实现了,它先将线路功率因数校正(PFC)电压降至电源盒外的母线电压,再降至主板的通用低电压, 这充分展示了新的高电压和大电流半导体技术及其架构的效用。

谐波极限值和功率因数校正

当电气负载(如PC)消耗的电流与输入电压(AC线路)同相,且电流不失真(正弦波)时,交流电网的功率输出可达到最佳状态。为此,作为欧洲标准的IEC 6100-2-3规定了各类设备的谐波极限值。例如,所有消耗功率超过75W的个人电脑的谐波(度数 n=3、5、...至39) 都必须处于或低于给定的曲线(以mA/W为单位)。目前,台式机的功耗在140W至250W之间,这意味着所有销售到欧洲的PC都必须符合上述标准。当这项标准确立后,世界其它地区都将逐步按照其执行。

另一方面,功率芯片制造商正不断开发能够处理高电压和大电流的技术。将交流电网电压转换至中间母线需可靠的设备提供数百伏电压和数安培电流。同时,再由母线电压转换至最终负载电压则需要数百安培电流的低压设备。上述功率转换已在个人电脑上实现了,它先将线路功率因数校正(PFC)电压降至电源盒外的母线电压,再降至主板的通用低电压, 这充分展示了新的高电压和大电流半导体技术及其架构的效用。

谐波极限值和功率因数校正

当电气负载(如PC)消耗的电流与输入电压(AC线路)同相,且电流不失真(正弦波)时,交流电网的功率输出可达到最佳状态。为此,作为欧洲标准的IEC 6100-2-3规定了各类设备的谐波极限值。例如,所有消耗功率超过75W的个人电脑的谐波(度数 n=3、5、...至39) 都必须处于或低于给定的曲线(以mA/W为单位)。目前,台式机的功耗在140W至250W之间,这意味着所有销售到欧洲的PC都必须符合上述标准。当这项标准确立后,世界其它地区都将逐步按照其执行。

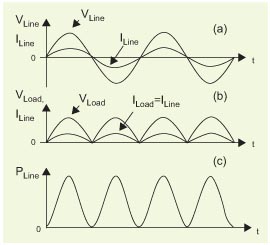

电源线路(PLINE=VLINE*ILINE)具有双倍频率 谐波越高, 限制越严格。但这些谐波的能量也越少,更易于滤波。根据该规范,允许谐波电流的最大输出大于600W,这样要在更高功率下符合这一规范就更具挑战性。 功率因数(PF)是与线路提供功率的综合质量相关的一个总体参数,它与输入电流总谐波失真(THD)的关系如下式所示: PF = cos( /(1+THD2)1/2 [1] 式中(是线路电压和消耗电流间的相位差。无相位差((=0),且无失真(THD=0)时, PF=1。由于分子(cos( (在0到1之间, 而分母总是大于或等于1,因而PF (=1。 由于IEC 61000-3-2标准规定了THD的谐波分量,THD和PF因此都不足以度量性能。实际上,这一规范的度量和遵从标准为谐波失真参数,这个参数以及达到这一规范的技术一般被划分到"PFC"或"功率因素校正"的类别中。 理论上,PF表达式中的cos( 既可为正,也可为负。请记住,负的cos( 值相当于负载电路对线路供电的情形。在基于二极管桥的整流电路中,这种情形是不可能发生的。 谐波极限值规范的约束 将功率从交流电网引至负载的标准方法是直接在负载两端跨接二极管桥整流器。如以由二极管桥式整流器和阻抗负载组成的简单系统为例,桥后的电压和电流则不失真,无相位差,可整流为正弦波,且PF=1 (图1)。在这种情况下,输入到负载上的功率由倍频、零最小和瞬时值波形构成: P(t)= (V2/R)*sen2(t = (1/2)*(V2/R)*(1-cos2(t) [2] 式中V是线路电压的幅度,R为负载,(为线路的角频率2(f,f=50Hz或60Hz。由方程[2]可得实际或平均的功率为: PAVE=(1/2)*V2/R = VRMS2/R [3] 随时间变化的零平均脉动功率为: PPΜLS = -(1/2)*(V2/R)*cos2(t [4] 这个简单例子描述了理想的AC线路整流电路模型。而另一方面,该电路没有能量存储功能,整流器输出端功率具有AC线路的倍频分量。在这一理想化的模型中,典型的负载实际上需要恒定(DC)功率。因此,它必须具有大容量的能量存储元件,一般采用处理非失真输入功率P(t)和DC输出功率PAVE差异的电解电容来实现。这个差异自然是由[4]所给出。

|