开关电容低通滤波器的设计

摘要:为了滤除信号中掺杂的高频噪声,设计一种六阶级联式开关电容低通滤波器,以数据采样技术代替传统有源RC滤波器中的大电阻,有利于电路的大规模集成。滤波器由双二阶子电路级联而成,电路中的电容值利用动态定标技术计算确定。用Hspice进行仿真验证,结果表明:开关电容低通滤波器能较好地时信号进行整形,其频率特性符合设计指标。

滤波技术是信号分析和处理中的重要分支,它的作用是从接收到的信号中提取有用的信息,抑制或消除无用的或有害的干扰信号,有助于提高信号完整度和系统稳定性。滤波器正是采用滤波技术的具有一定传输选择性的信号处理装置。随着现代集成电路技术和MOS工艺的飞速发展,模拟集成滤波器的实现已经成为现代工业的一个重大课题,也是当今国际上的前沿课题。

传统的连续时间模拟滤波器采用有源RC结构,能够应用到较高的频率,但是电路中多采用大电容和大电阻,在集成电路制造时会占用大量的芯片面积。在现代集成电路工艺中,很难得到精确的电阻值和电容值,而且电阻值随温度变化很大,精度只能达到30%.

1972年,美国科学家Fried发表了用开关和电容模拟电阻R的论文,由此开关电容技术成为模拟集成滤波器设计中常用的方法。开关电容滤波器是由运算放大器、电容器和MOS开关组成的有源开关电容网络,以数据采样技术代替大电阻,减小了芯片的面积和功耗,且电路的极点和时间常数由电容的比值确定,可实现高精度的模拟集成滤波器。本文设计一种开关电容低通滤波器,用于滤除有用信号中掺杂的高频噪声。

1 开关电容技术的原理

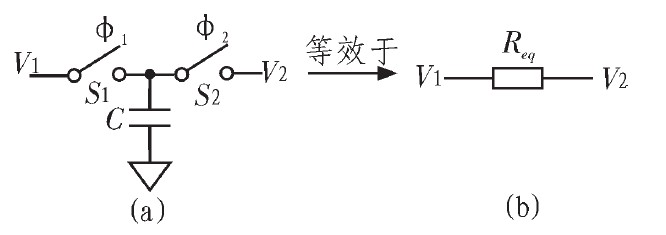

图1中的开关电容等效电阻电路由两个独立的电压源V1、V2,两个受控开关S1、S2和电容C组成。开关S1和S2受两相不交叠的时钟φ1和φ2控制,时钟频率均为fs。

图1 开关电容等效电阻电路

在时钟φ1和φ2的控制下,两个开关周而复始地闭合与断开。φ1闭合时,C充电到V1,φ2闭合时,C放电到V2,传输的总电荷为C(V1-V2),流向V2的平均电流为:

I=Qfs=C(V1-V2)*fs (1)

根据欧姆定律,可知此开关电容电路的等效电阻(如图1(b)所示)为:

Req=1/Cfs (2)

利用开关电容等效电阻电路的最大优点是节省了硅片面积。以图1(a)电路为例,若时钟频率为200 kHz,要模拟一个阻值为10 MΩ的大电阻,所需的电容值为0.5 pF,所消耗的硅片面积仅为标准CMOS工艺制成的硅成型电阻面积的1%.此外,开关电容模拟电阻的阻值容易调节,在对电路原有结构几乎不做任何改动的前提下,仅通过调整电容的比值就能改变整体电路的参数。

2 低通滤波器的总体设计

文中设计的低通滤波器主要用于滤除有用信号中的高频噪声,截止频率为20 kHz,开关电容采样时钟频率为1 MHz,其设计指标如表1所示。

表1 开关电容低通滤波器设计指标

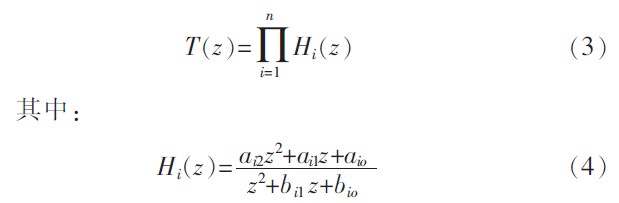

根据滤波器设计指标的要求,文中设计一种六阶低通滤波器,采用级联式开关电容滤波器的设计方法,也就是直接将低阶滤波器连接起来而确定高阶滤波器的传递函数。高阶滤波器(高于3阶)主传递函数的分子和分母被分解成一阶或二阶子函数,每个低阶滤波器都具有各自的缓冲电路,级联在一起不会相互影响,调试电路时易于发现问题。

高阶滤波器的传输函数是指整个滤波器的输出电压和输入电压的比值,从电路设计的灵敏度和复杂度来看,采用级联双二阶的方法来实现高阶滤波器比较合适,它的一般形式为:

摘要:为了滤除信号中掺杂的高频噪声,设计一种六阶级联式开关电容低通滤波器,以数据采样技术代替传统有源RC滤波器中的大电阻,有利于电路的大规模集成。滤波器由双二阶子电路级联而成,电路中的电容值利用动态定标技术计算确定。用Hspice进行仿真验证,结果表明:开关电容低通滤波器能较好地时信号进行整形,其频率特性符合设计指标。

滤波技术是信号分析和处理中的重要分支,它的作用是从接收到的信号中提取有用的信息,抑制或消除无用的或有害的干扰信号,有助于提高信号完整度和系统稳定性。滤波器正是采用滤波技术的具有一定传输选择性的信号处理装置。随着现代集成电路技术和MOS工艺的飞速发展,模拟集成滤波器的实现已经成为现代工业的一个重大课题,也是当今国际上的前沿课题。

传统的连续时间模拟滤波器采用有源RC结构,能够应用到较高的频率,但是电路中多采用大电容和大电阻,在集成电路制造时会占用大量的芯片面积。在现代集成电路工艺中,很难得到精确的电阻值和电容值,而且电阻值随温度变化很大,精度只能达到30%.

- 电容感测:你应该选择哪个架构?(02-11)

- EMI噪声分析及EMI滤波器的设计(10-07)

- 单片机数字滤波的算法(10-12)

- 升压电源与高压天线和滤波器提供调谐信号(01-28)

- 自激式开关稳压电源的工作原理及功能设计(01-13)

- 充电电源怎么样轻松估计负载瞬态响应的方法(04-18)