开关电容低通滤波器的设计

1972年,美国科学家Fried发表了用开关和电容模拟电阻R的论文,由此开关电容技术成为模拟集成滤波器设计中常用的方法。开关电容滤波器是由运算放大器、电容器和MOS开关组成的有源开关电容网络,以数据采样技术代替大电阻,减小了芯片的面积和功耗,且电路的极点和时间常数由电容的比值确定,可实现高精度的模拟集成滤波器。本文设计一种开关电容低通滤波器,用于滤除有用信号中掺杂的高频噪声。

1 开关电容技术的原理

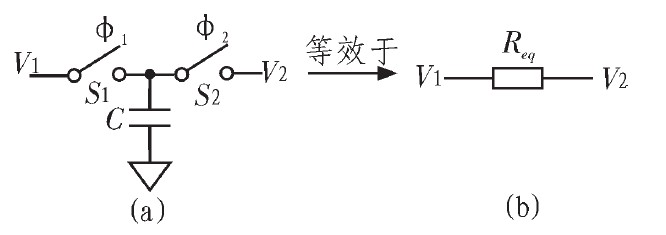

图1中的开关电容等效电阻电路由两个独立的电压源V1、V2,两个受控开关S1、S2和电容C组成。开关S1和S2受两相不交叠的时钟φ1和φ2控制,时钟频率均为fs。

图1 开关电容等效电阻电路

在时钟φ1和φ2的控制下,两个开关周而复始地闭合与断开。φ1闭合时,C充电到V1,φ2闭合时,C放电到V2,传输的总电荷为C(V1-V2),流向V2的平均电流为:

I=Qfs=C(V1-V2)*fs (1)

根据欧姆定律,可知此开关电容电路的等效电阻(如图1(b)所示)为:

Req=1/Cfs (2)

利用开关电容等效电阻电路的最大优点是节省了硅片面积。以图1(a)电路为例,若时钟频率为200 kHz,要模拟一个阻值为10 MΩ的大电阻,所需的电容值为0.5 pF,所消耗的硅片面积仅为标准CMOS工艺制成的硅成型电阻面积的1%.此外,开关电容模拟电阻的阻值容易调节,在对电路原有结构几乎不做任何改动的前提下,仅通过调整电容的比值就能改变整体电路的参数。

2 低通滤波器的总体设计

文中设计的低通滤波器主要用于滤除有用信号中的高频噪声,截止频率为20 kHz,开关电容采样时钟频率为1 MHz,其设计指标如表1所示。

表1 开关电容低通滤波器设计指标

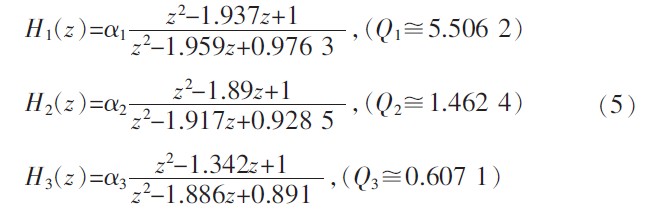

根据滤波器设计指标的要求,文中设计一种六阶低通滤波器,采用级联式开关电容滤波器的设计方法,也就是直接将低阶滤波器连接起来而确定高阶滤波器的传递函数。高阶滤波器(高于3阶)主传递函数的分子和分母被分解成一阶或二阶子函数,每个低阶滤波器都具有各自的缓冲电路,级联在一起不会相互影响,调试电路时易于发现问题。

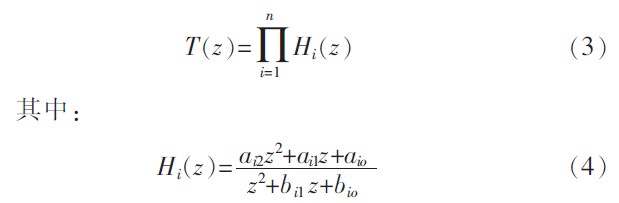

高阶滤波器的传输函数是指整个滤波器的输出电压和输入电压的比值,从电路设计的灵敏度和复杂度来看,采用级联双二阶的方法来实现高阶滤波器比较合适,它的一般形式为:

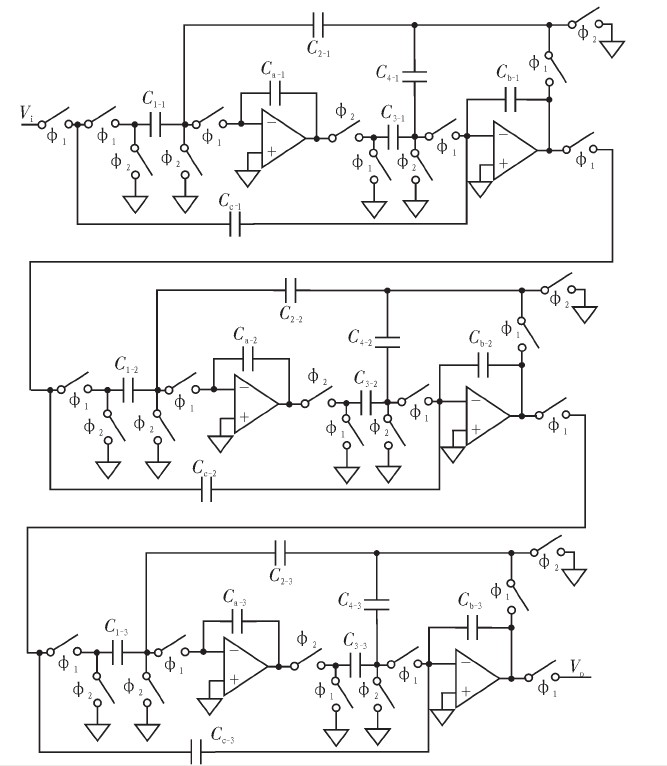

利用表1中设计指标进行计算,得到滤波器传递函数的所有零极点值,并进行配对。令z平面上最靠近单位圆的极点拥有最高的优先级,优先同与其最靠近的零点首先配对,然后是其次最靠近单位圆的极点进行零点的选择,依次类推,得到各双二阶子电路的传递函数:

双二阶传递函数的Q值分配会影响整体电路的性能:如果第1级的Q值过高,可能导致较大的电容分布和较高的敏感性,因为其中最敏感的极点(即靠近单位圆的极点)没有与某个与之相近的零点配对;而最后1级的Q值较高将会在拐角频率附近引起一些尖峰。由于设计的滤波器阶数为6,将具有高Q值的H1(z)放在中间,即第1级和第3级使用的是低Q双二阶电路,中间级第2级使用的是高Q电路。六阶级联式开关电容低通滤波器的整体电路如图2所示。

图2 六阶级联式开关电容低通滤波器的整体电路

3 电路中电容值的计算

根据公式(5)计算电路中的电容值,使用动态范围定标技术对每个运放的输出电压幅值进行缩放,使得所有运放能够在同样的输入电平下饱和,从而开关电容滤波器能够在尽可能大的输入动态范围内工作。具体方法是:增大输入电压Vi直到滤波器的输出处于临界饱和状态,计算这个状态下每个内部运放的输出电压,然后将连接到每个运放输出接点的所有电容乘以相应运放的输出电压值,然后将对连接到每个运放输入端的所有电容进行最小化或缩放,使其中的最小电容(非零值)归一化为1,对系统中所有运放依次重复这个处理步骤,得到定标后的电容值。

文中模拟仿真实现时所用的运放为理想运放,输出峰值无上限,因此定标过程对连接到每个运放输入端的电容进行缩放,由设计目标知最小电容为0.5 pF,可得到定标后的电容值在表2中列出。

表2 定标后的电容值

4 仿真结果

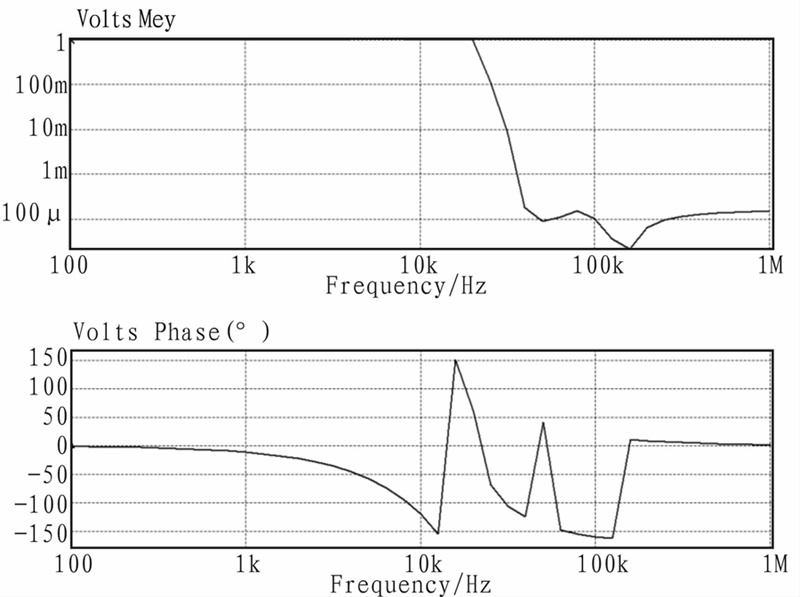

用Hspice软件对设计的开关电容低通滤波器进行仿真,图3为文中设计的开关电容低通滤波器的幅频特性及相频特性。由图中可以看出截止频率为20 kHz左右,且通带内波纹不明显,衰减明显,满足设计目标。

图3 滤波器的频率特性

为了更好地验证设计出的低通开关电容滤波器在实际滤波应用中的性能,文中给输入端加带有高频分量的磁通门探头信号,检验电路的滤波效果。

在图4中,上图输

- 电容感测:你应该选择哪个架构?(02-11)

- EMI噪声分析及EMI滤波器的设计(10-07)

- 单片机数字滤波的算法(10-12)

- 升压电源与高压天线和滤波器提供调谐信号(01-28)

- 自激式开关稳压电源的工作原理及功能设计(01-13)

- 充电电源怎么样轻松估计负载瞬态响应的方法(04-18)