一种高速低功耗LVDS接收器电路的设计

摘要 介绍了LVDS系统链路结构及数据传输原理,分析了LVDS标准对接收器电路的需求,文中基于65 nm数字CMOS工艺设计,实现了一种高速低功耗LVDS接收器电路。仿真结果表明,在2.5 V电源电压工作下,该LVDS接收器具有2 Gbit·s-1的数据传输速率,平均功耗为3 mW。

关键词 低压差分信号(LVDS);接收器;差分信号;高速

随着高清多媒体处理器、高性能数字信号处理器和网络终端技术的发展,数据传输速率的要求越来越高。集成电路工艺的快速发展使得芯片内部千兆比特每秒数据传输速率成为可能,然而芯片与芯片之间、不同系统终端之间的传统接口电路,成为制约整个系统数据传输速率提高的障碍。

低电压摆幅差分信号(Low Voltage Differential Signal,LVDS)接口,是20世纪90年代提出的一种高速数据传输和接口技术,由美国国家半导体公司率先提出,并于1996年通过为IEEE标准。其核心是采用低电压摆幅高速差分地传输数据,LVDS技术可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点。目前LVDS接口电路广泛集成在高速ADC、DSP等芯片内部解决高速数据传输的接口问题。

1 LVDS系统链路原理及接收器电路分析

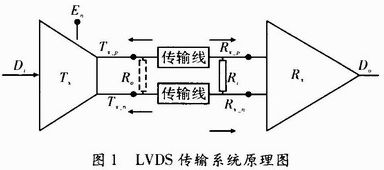

LVDS传输系统原理如图1所示,发送器将输入的CMOS电平的数字信号转换成差分LVDS信号进行通信传输,差分信号通过传输线到达接收器电路,接收器电路将差分LVDS信号转换成CMOS信号供后续数字处理电路处理。在信号传输线的输入和输出端,考虑到高频信号的反射需要阻抗匹配电阻。在LVDS系统中,信号差分驱动输出,在接收端连接一个100 Ω的电路以匹配传输线上单端阻抗50Ω。

由于发送器和接收器系统间通常距离较远,互连线电阻会引入共模电平变化;而且LVDS为全差分传输,噪声通常以共模噪声的形式耦合到传输线上,为提高噪声容限,IEEE Std.1596.3-1996(LVDS)标准对接收器输入共模电平的变化允许1 V。同时,为了消除输入信号的不确定性,接收器的输入要求有约25 mV的迟滞。因此接收器电路一般包括一个宽共模范围的前置放大器和迟滞比较器。根据模拟集成电路设计规则,接收器需要在各种PVT条件下满足LVDS标准对接收电压阈值VTH,IN输入差分迟滞电压VHyst和输入共模电平VCM,IN的规定如下

|VTH,IN|≤100mV

VHyst≥25mV

0≤VCM,IN≤2.4V

2 接收器电路设计

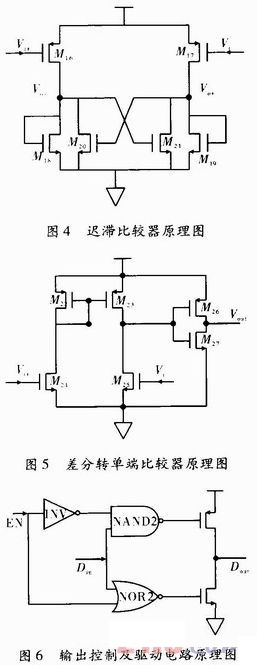

新型低功耗接收器电路原理如图2所示。该接收器电路有Rail-rail前置放大器、迟滞比较器、差分转单端比较器和逻辑控制及驱动电路组成。其中Rail-rail前置放大器的原理如图3所示,该前置放大器由Rail-rail输入差分对构成的折叠式运算放大器组成;Rail-rail输入差分对保证了宽共模范围的输入,折叠式共源共栅输出阶电路保证了增益需求的同时具有较宽的输入信号带宽,满足高速信号传输的要求;输入差分对的微电流源以及负载电流源偏置由输出共模电压提供,既降低了功耗又简化了偏置电路。迟滞比较器的原理如图4所示,该迟滞比较器由伪差分输入对和二极管负载以及负阻二极管构成。差分输入迟滞电压由二极管负载管M18和负阻二极管M20的尺寸决定。

差分转单端比较器原理如图5所示,该比较器由伪差分输入对和电流镜像负载构成,同时增加了反相器驱动。逻辑控制和输出驱动电路原理如图6所示,当输出控制逻辑EN为高电平时,输出驱动管均关断,输出节点为高阻输出模式;当输出控制逻辑EN为低电平时,输出信号随输入信号的改变而变化。

摘要 介绍了LVDS系统链路结构及数据传输原理,分析了LVDS标准对接收器电路的需求,文中基于65 nm数字CMOS工艺设计,实现了一种高速低功耗LVDS接收器电路。仿真结果表明,在2.5 V电源电压工作下,该LVDS接收器具有2 Gbit·s-1的数据传输速率,平均功耗为3 mW。

关键词 低压差分信号(LVDS);接收器;差分信号;高速

随着高清多媒体处理器、高性能数字信号处理器和网络终端技术的发展,数据传输速率的要求越来越高。集成电路工艺的快速发展使得芯片内部千兆比特每秒数据传输速率成为可能,然而芯片与芯片之间、不同系统终端之间的传统接口电路,成为制约整个系统数据传输速率提高的障碍。

低电压摆幅差分信号(Low Voltage Differential Signal,LVDS)接口,是20世纪90年代提出的一种高速数据传输和接口技术,由美国国家半导体公司率先提出,并于1996年通过为IEEE标准。其核心是采用低电压摆幅高速差分地传输数据,LVDS技术可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点。目前LVDS接口电路广泛集成在高速ADC、DSP等芯片内部解决高速数据传输的接口问题。

1 LVDS系统链路原理及接收器电路分析

LVDS传输系统原理如图1所示,发送器将输入的CMOS电平的数字信号转换成差分LVDS信号进行通信传输,差分信号通过传输线到达接收器电路,接收器电路将差分LVDS信号转换成CMOS信号供后续数字处理电路处理。在信号传输线的输入和输出端,考虑到高频信号的反射需要阻抗匹配电阻。在LVDS系统中,信号差分驱动输出,在接收端连接一个100 Ω的电路以匹配传输线上单端阻抗50Ω。

- LVDS的接口电路设计(02-26)

- 如何用单个赛灵思FPGA数字化数百个信号(04-30)

- 赛灵思FPGA中LVDS差分高速传输的实现(02-11)

- 基于极零点灵敏度的模拟电路可测性分析(09-15)

- 利用高端电流检测放大器简化模拟电路设计(09-15)

- 高可靠DC/DC变换器模块设计(09-15)