高速脉冲峰值保持电路的设计

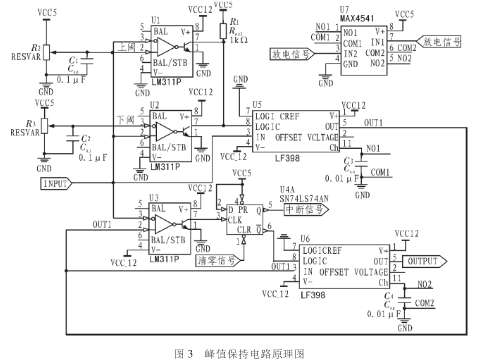

3 电路调试

3.1 保持电容的选取

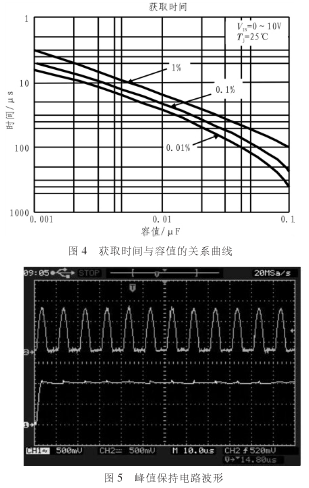

保持电容对于电路精度具有很大影响。电容及其容值的选择应综合考虑下降误差、采样保持偏差、采样频率、精度等指标。保持电容产生误差的主要原因是感应吸收,即电容两端在电压急剧变化时,产生电容值下降的现象。经测试发现:电容两端电压在1μs内由10 V降至100 mV时,聚脂薄膜电容约变化0.8%,陶瓷电容变化在1%以上,本电路中保持电容C3、C4选用感应吸收与漏电流均较小的聚苯乙烯电容。容值的选取参照如图4所示曲线。容值选的过小,则峰值保持时间会缩短;选的过大,则电容充放电时间过长。综合以上因素,C3、C4电容值取0.01μF。

3.2 尖峰电压的消除

在凋试过程中笔者发现,当电路由采样状态切换到保持状态的瞬间,输出端产生了尖峰电压。起初,笔者降低输入逻辑输入信号的幅度(由12 V降低到1 V),但尖峰电压并没有很好的消除。经过对于LF398各管脚间耦合情况的分析测试得出:尖峰电压是由于LF398进入保持状态的同时,逻辑输入信号通过电路板布线间寄生电容耦合和漏电耦合到模拟信号输入端引起的。假设逻辑输入端(也就是LOGIC引脚)与保持电容存在着1 pF的寄生电容,保持电容是0.01μF,那么当逻辑输入端由0 V跳变到5 V,LF398从采样状态切换到保持状态时,相当于在模拟输入端增加了约1 mV的输入信号,因而会在输出端产生尖峰。可以采取以下措施消除尖峰:一是在布线时逻辑输入端走线与模拟输入端走线尽可能远些;二是将模拟输入端用地线包围起来,降低线间寄生电容耦合和漏电耦合干扰。

4 实验结果

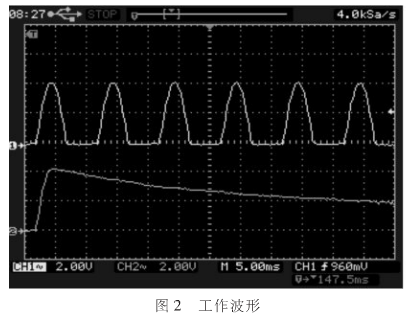

为验证文中电路的可行性,用盛谱科技公司的F05型任意波信号发生器产生幅度为1V、频率为100 kHz的脉冲信号作为输入,用同惠电子公司的TD01000型双通道示波器观察输入输出电压波形,如图5所示,波形1为峰值保持电路输入信号波形,波形2为峰值保持稳定后的信号波形。从图中可以看出,文中设计的峰值保持电路较好地保持了输入信号的峰值,起伏较小。电路保持住的峰值与输入信号峰值误差<1%,满足A/D转换的要求。

5 结束语

文中介绍了采用电压比较器LM311,采样/保持芯片LF398集成芯片等构成的峰值保持电路,结构简单、成本低廉、易于调试。实验表明,该电路性能可靠、稳定性好、可以有效地克服温漂,灵敏度好,误差小于<1%,可用于高速脉冲信号的峰值甄别保持,下一步将致力于提高电路在复杂环境下的峰值保持的有效性,提高电路的抗干扰能力。

- 基于极零点灵敏度的模拟电路可测性分析(09-15)

- 利用高端电流检测放大器简化模拟电路设计(09-15)

- 高可靠DC/DC变换器模块设计(09-15)

- 水平枕形校正电路(10-09)

- 混合集成电路的电磁兼容(EMC)设计 (10-07)

- 家电智能功率模块单驱动电源方案(10-07)