高速脉冲峰值保持电路的设计

摘要:为满足能谱分析中多道脉冲幅度分析器A/D转换的要求,设计了一种高速脉冲峰值保持电路。以高速电压比较器LM311、采样/保持芯片LF398作为主要器件,具有幅度判别、波形采样、峰值保持、电荷泄放等功能,结构简单,易于调试。实验表明:对于高速脉冲信号,该电路可以较好地甄别峰值并保持,性能可靠,响应速度快,误差小于1%。

关键词:高速脉冲;峰值保持电路;LM311;LF398

在能谱测量中,多道脉冲幅度分析器所测量的是脉冲的峰值幅度,但探测器输出信号经过线性放大后的脉冲信号峰顶很窄,即使经过理想最佳滤波器将窄脉冲调理成信噪比很高的高斯脉冲,仍不能满足多道脉冲幅度分析特别是A/D转换的要求。这时必须由脉冲峰值保持电路将脉冲峰值甄别并展宽,使脉冲的峰值保持一段时间再送入后续电路。因此,峰值保持电路又叫做模拟展宽器。笔者采用集成芯片设计了一种适用于高速脉冲信号的峰值保持电路,对于100 kHz的模拟信号,峰值保持电路可以准确地采集到峰值并保持,同时向单片机发出请求中断信号,启动A/D转换器。A/D转换完成后,保持电容迅速放电,等待下一个脉冲的到来。

1 峰值保持理论

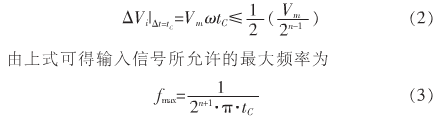

峰值保持电路具有保持和采样2个状态。处于采样状态时,电路的输出始终跟随输入信号;处于保持状态时,电路的输出保持着前一次采样结束前瞬间的输入模拟量。在高速脉冲峰值采集过程中,为保证A/D转换精度,在转换过程中其输入信号变化量不能大于1/2 LSB。假设输入信号Vi=Vmsinωt,则Vi的最大变化率为

当A/D转换器的分辨率为n位,转换时间为tc时,为保证A/D转换器的正常工作,则

设8位A/D转换器的转换时间tc=100μs,代入上式计算可得,A/D转换器的所允许的最大输入信号频率fmax=6 Hz。为获取高频的脉冲信号峰值,必须存信号输入A/D转换器之前对其峰值进行保持。

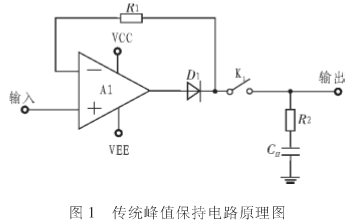

传统的峰值保持电路原理图如图1所示,由集成运算放大器,二极管和电容构成。图2为其工作波形,其中波形1为输入信号波形,波形2为开关K1打开后峰值保持的波形。

在传统的峰值保持电路中,输入信号通过由运算放大器组成的电压跟随器后向保持电容充电,直到充到输入电压的最大值。在理想情况下,保持电容可以保持输入信号的峰值电压,但是实际中二极管的反向电阻不是无穷大,电路下一级也存在电阻并且保持电容存在漏电。从频域来看,二极管和保持电容组成的网络积分非线性大、动态范围小且存在极点,由于二极管内部电阻不是恒定值,极点的位置不固定。通过这样的电路采集到的峰值信号,不能够满足高速脉冲信号处理的要求。为了克服以上缺点,前人做了大量工作,其中文献设计了由肖特基二极管和跨导放大器组成的峰值保持电路,取得了较好效果,但是仍存在对于高速窄脉冲信号响应不灵敏、精度低等不足。本文旨在提出并设计一种适用于高速脉冲信号的峰值保持电路。

2 电路原理

图3是峰值保持电路原理图,该电路主要由幅度判别、波形采样、峰值保持、电荷泄放等部分组成,幅度判别采用高速低功耗电压比较器LM311实现,电压上阈、下阈由可调精密电位器分压获得。由于LM311输出端集电极开路,将U1,U2输出端接上拉电阻可实现"线与"功能;采用NationalSemiconductor公司的采样保持芯片IF398实现采样/保持功能,其控制端可直接接于TTL、CMOS逻辑电平,LOGIC引脚电平决定电路处于采样/保持状态。模拟开关MAX4541接收单片机控制信号,控制保持电容C3、C4充放电。若输入信号Vi幅度处于上下阈之间,U1、U2同时输出高电平,"线与"后得到高电平送到U5的LOGIC管脚,U5处于采样状态,输出OUT1跟随输入信号Vi变化。峰值没有到来时,OUT1<Vi,比较器U3输出低电平,D触发器U4不触发,A/D转换不启动,模拟开关U7断开,电容充电。当峰值到来时,U1、U2、U5状态不变,而由于OUT1>Vi,U3输出高电平,产生上升沿,D触发器U4被触发,/Q输出低电平,U6处于保持状态,将OUT1输出的峰值保持住,并送至A/D转换器;同时Q输出高电平,向单片机发送中断信号,通知单片机峰值到来,单片机收到中断信号后启动A/D转换。A/D转换完成后,单片机向D触发器发出清零信号,同时控制模拟开关U7闭合,保持电容C3,C4放电,等待下一个脉冲的到来。

- 基于极零点灵敏度的模拟电路可测性分析(09-15)

- 利用高端电流检测放大器简化模拟电路设计(09-15)

- 高可靠DC/DC变换器模块设计(09-15)

- 水平枕形校正电路(10-09)

- 混合集成电路的电磁兼容(EMC)设计 (10-07)

- 家电智能功率模块单驱动电源方案(10-07)