应用于负电源的电平位移电路及器件设计

(c)为nLDMOS的关态耐压、开态耐压及阈值与体区注入剂量(Pbody)的关系。可以看出增加体区的注入剂量对器件的耐压影响很校但是随着注入剂量的增加,体区浓度增加,所以阈值就增加,同时器件的开态耐压也随之增加。当体区注入剂量达到5e14cm-2时,阈值增加缓慢,开态耐压却大幅增加,所以只能通过阈值上的牺牲来改善nLDMOS的开态击穿耐压。

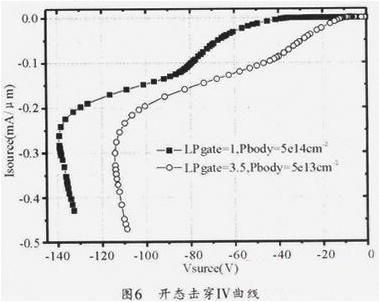

通过以上分析,发现提高nLDMOS的开态击穿电压最有效的方法是缩短栅极场板和提高体区注入剂量。这二种方法的实质提高导通阻抗或降低电流能力。但是对于普通应用的nLDMOS,电流能力本身就比pLDMOS有优势。当应用到负电源电平位移电路中时,厚栅氧高栅源电压使得nLDMOS的电流能力更加突出,但是同时也导致了开态耐压的降低。所以提高nLDMOS开态击穿电压就必须降低其电流能力。如图6所示,在nLD-MOS正常工作时,源端的电压为-100V,此时饱和电流相差0.05mA/μm。

在缩短栅极场板到1μm,提高体区注入剂量到5e14 cm-2的情况下,在得到nLDMOS的阈值电压为24V,关态击穿电压215V,开态击穿电压140V,能够满足-100V电压的应用要求。

3 结束语

本文设计一种应用于8~-100V电源的电平位移电路。通过在常规正电源电平位移电路的基础上改变低压控制方式来实现从0~8V低压逻辑输入到8~-100V高压驱动输出的转换。基于此电路结构设计了满足电路应用需求的高压器件。并对高压LDMOS进行了优化设计,尤其是高压nLDMOS的开态耐压。得到高压nLDMOS的关态击穿电压215V,开态击穿电压140V,阈值电压24V;高压pLDMOS的关态击穿电压200V,开态击穿电压160V,阈值电压-1V。

- 单电源供电回路中获得正负电源的原因(11-24)

- 凌力尔特专家解析负电源轨不会消失的原因(10-11)

- 基于SOI高压集成技术的电平位移电路设计(09-06)

- 基于极零点灵敏度的模拟电路可测性分析(09-15)

- 利用高端电流检测放大器简化模拟电路设计(09-15)

- 高可靠DC/DC变换器模块设计(09-15)