一种200V/100A VDMOS 器件开发

备片→薄氧氧化→ SiN 淀积→一次光刻→刻蚀→场氧化→ SiN 剥离→栅氧氧化→多晶硅淀积→ 多晶硅掺杂→二次光刻→多晶硅刻蚀→中剂量硼(P-)注入→三次光刻→大剂量硼(P+)注入→ P 阱推进→四次光刻→大剂量磷(N+)注入→PSG淀积→PSG致密→五次光刻→接触孔刻蚀→金属化→ 六次光刻→金属刻蚀→合金→钝化介质淀积→七次光刻→刻蚀→原片减薄→背面金属化→测试上述流程中,栅氧化、第三、四、五次光刻与第二次光刻套准、多晶硅刻蚀、P 阱推进等为关键工艺,需要重点监控,其余工艺均相对成熟。

表1 栅氧化工艺条件

3.1 栅氧化

质量较好的栅氧,其击穿特性为本征击穿,通常厚度为10nm的氧化层其击穿电压需达到8V以上。

除了热氧化工艺本身外,氧化前处理也是重要环节。

此处采用SC3 液和HF溶液处理,完成后冲水、甩干,入扩散炉管进行热氧化,加工条件如表1 所示。氧化完成后,用膜厚仪测试得到膜厚平均值为100 ±3nm,均匀性良好。

3.2 光刻套准

平面型VDMOS N+ 源区、P+ 注入区、欧姆接触孔等位置在元胞内通常呈中心对称,如图1 所示,这是器件电学特性一致性和可靠性的要求。由于自对准工艺采用多晶硅刻蚀后的图形作为P- 注入掩蔽,其后的N+ 注入掩蔽需要位于多晶硅刻蚀窗口的中心位置,P+ 注入光刻和欧姆接触孔光刻后形成的窗口也需要位于该区域中心。上述要求除了版图设计时的精确度量以外,加工过程中的实际套准也至关重要。通常采用数套游标图形以监控光刻工艺中的套准,本次设计采用第三、四、五图层游标对套第二层游标的方法,光刻显影后的实际套准状况如图2所示。可见第四次光刻(NLS)与第二次光刻(PLY)套准良好,X 和Y 方向的误差不超过0.1 μm。第三层与第五层也有类似结果,此处不再一一列出。

图2 NLS 光刻与PLY光刻套准游标

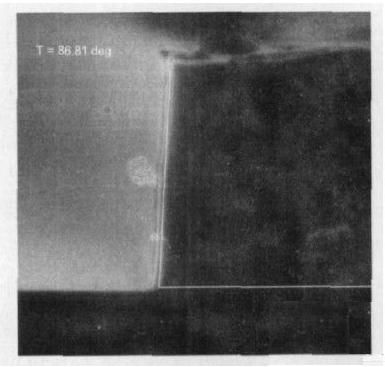

3.3 多晶硅刻蚀

多晶硅栅自对准工艺要求作为P- 注入掩蔽的多晶硅覆盖区边缘光滑、侧壁陡直,因此通常采用干法刻蚀工艺形成多晶硅刻蚀窗口,其中刻蚀气氛、射频功率、真空度等条件对刻蚀速率、均匀性、各项异性效果影响很大。采用HITACHI M-206 II 设备,首先以一定比例SF6 和CHF3 混合气体去除多晶硅表面氧化层,然后用Cl2 和HBr 混合气体刻蚀多晶硅及部分栅氧层。由图3 可见,采用上述条件刻蚀多晶硅,可以得到接近87°的侧壁角度,表面光滑齐整;尤其重要的是,刻蚀完成后的剩余栅氧厚度较为均匀,控制在500 ± 50 μm 的范围,有利于后续P- 和N+ 注入的均匀性。

图3 干法刻蚀多晶硅图片

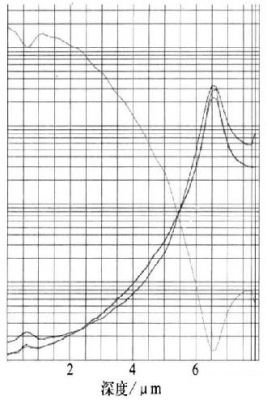

3.4 P阱推进

导电沟道形成于P 阱表面,该处杂质分布是决定器件阈值电压的关键参数之一,而且,P 阱深度及杂质扩散轮廓与元胞和场限环击穿电压密切相关,也是器件抗雪崩击穿能力的决定性参数。尽管设计良好的器件对于P 阱推结工艺有一定容差,此工序仍应重点监控。采用1150℃,纯N2条件下推进330min,得到的结深约6.5 μ m,扩展电阻法测试结果如图4所示。

图4 P 阱扩展电阻测试曲线

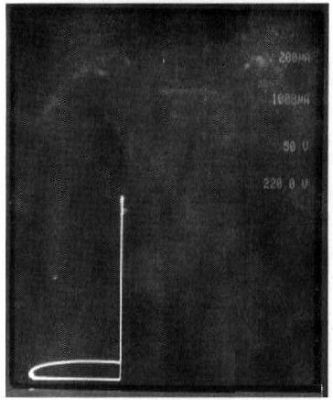

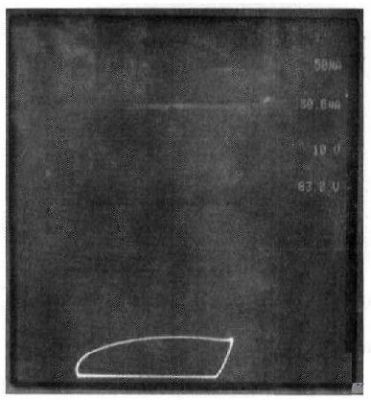

4 测试结果

流水所得芯片如图5 所示,面积14400 μ m ×10800μm,其中左边两个角上深色方块为栅极压点,中间区域七个深色图形为源极压点。采用JU NODTS1000 系统测试结果如表2 所示,各参数良好,其中RDS(on)和Vsd 均为脉冲测试。图6 为元胞扫描电镜图片,其中N 阱、P 阱及多晶硅下的"鸟嘴"清晰可见,后者显着减小了该区域栅电容。图7、图8 分别为Tektronics 371 晶体管图示仪测试所得漏源击穿电压和栅源耐压波形,可见器件漏源击穿特性良好,栅源耐压大于83V,达到本征击穿。

图5 200V/100A芯片照片

图6 元胞扫描电镜分析

图7 漏源击穿电压波形

图8 栅源耐压波形

表2 200V/100A VDMOS器件参数测试结果

5 结论

本文采用圆弧形分布沟道与局域氧化相结合的方法开发出一种200V/100A VDMOS器件,在一定程度上解决了器件导通电阻改善与开关损耗增大的矛盾。对流水过程中的关键工艺进行了监控,所得器件具有较好的综合性能, 为国产大电流功率MOSFET 器件研发探索出一条途径。

- 凌力尔特大功率多相同步升压型DC/DC控制器LTC3787(10-15)

- 电动自行车控制器MOSFET驱动电路的设计(11-18)

- 两种常见的MOSFET驱动电路设计(12-02)

- 集成MOSFET 的分立器件方案(01-30)

- 功率MOSFET的锂电池保护电路设计(04-18)

- 提升电源转换效率的自定时电压检测同步MOSFET控制方案(10-11)