一种200V/100A VDMOS 器件开发

摘 要:分析了功率MOSFET 最大额定电流与导通电阻的关系,讨论了平面型中压大电流VDMOS器件设计中导通电阻、面积和开关损耗的折衷考虑,提出了圆弧形沟道布局以增大沟道宽度,以及栅氧下部分非沟道区域采用局域氧化技术以减小栅电容的方法,并据此设计了一种元胞结构。详细论述了器件制造过程中的关键工艺环节,包括栅氧化、光刻套准、多晶硅刻蚀、P 阱推进等。流水所得VDMOS 实测结果表明,该器件反向击穿特性良好,栅氧耐压达到本征击穿,阈值电压2.8V,导通电阻仅25m Ω,器件综合性能良好。

1 引言

功率金属- 氧化物- 半导体场效应晶体管(MOSFET)、绝缘栅双极晶体管(IGBT)、智能功率模块(IPM)被誉为新型电力电子器件的代表,广泛应用于工业控制、电力机车、家用电器、绿色照明、计算机、汽车电子等诸多领域。目前,我国功率MOSFET 产业已经初步形成,产品主要集中在60V~600V 中小电流范围,对于200V/100A以上的中高压大电流器件,尚未见到国产的成熟产品。这类器件主要应用于大功率DC-DC 换流器、同步整流、开关模式或谐振模式电源、DC 斩波器、电池充电等领域。基于扬州国宇电子有限公司5 英寸功率MOSFET 技术,本文提出了一种200V/100A VDMOS器件元胞结构,然后重点阐述了包括光刻、刻蚀、扩散等在内的关键制造工艺,最后对测试结果进行了分析。

2 器件结构

按照导电沟道相对于硅片表面的方向不同,功率MOSF ET 通常分为平面型VDMOS 和沟槽型TrenchMOS,二者均通过两次扩散在栅氧一侧形成长度不同的掺杂区域来构造导电沟道。由于沟槽刻蚀使得栅氧形成于纵向,极大地提高了硅片表面利用率,并消除了JFET 区,因而TrenchMOS器件横向尺寸得以显着减小,每平方厘米可达数千万个元胞,其精细程度已进入深亚微米范畴。不过,由于沟槽底部拐点区域固有的电场集中效应,TrenchMOS 主要应用于数十伏的低压领域,在150V~600V 的中高压范围内,平面型VDMOS 仍是主流。此外,平面型VDMOS 还具有工艺相对简单、成品率高的特点。

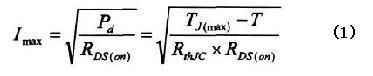

正向导通状态下,功率MOSFET 最大额定电流主要受限于功率耗散,即:

其中Pd 为功率耗散,RDS(on)为导通电阻,TJ(max)、T 分别为器件允许的最高工作温度和实际工作温度,RthJC 为器件热阻,与封装有关。可见,导通电阻是最大额定电流的决定性因素之一,在器件综合性能允许的情况下,最大程度地降低导通电阻是器件设计的关键环节,也是功率MOSFET 自上世纪八十年代出现以来,工程师们持之以恒的追求。2009年8月,美国Fairchild 公司开发出世界上首只导通电阻小于1m Ω的功率MOSFET,最大额定电压/ 电流为30V/60A,主要得益于高密度沟槽栅技术的采用使得单位面积内有更多元胞并联,增大了沟道总有效宽度,从而显着地减小了以沟道电阻为主的导通电阻。

对于中高压平面型VDMOS 器件来说,增加元胞数量以减小导通电阻也是有效的方式,一方面可以减小漂移区电阻和JFET 区电阻,另一方面也增大了总的沟道有效宽度,尽管沟道电阻可能不再是主要矛盾。不过,元胞数量的增加必然增大器件面积,最终受限于由栅电容决定的开关损耗, 因此,VDMOS 器件设计需要折衷考虑导通电阻和开关损耗,对外延层厚度、掺杂浓度、元胞结构、栅氧厚度、面积等参数进行优化。对于一定的阻断电压,采用增大元胞内沟道宽度以减小沟道电阻、增大多晶覆盖下的非沟道区域栅氧厚度以减小栅电容是减小器件功率耗散的有效途径。

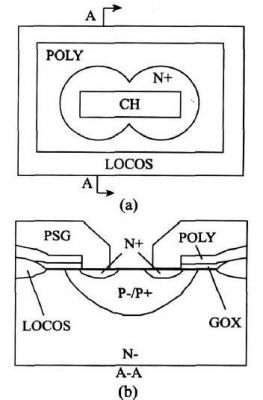

设计的器件元胞结构如图1 所示,图1(a)为元胞俯视图,图1(b)为A-A 处剖面示意图,其中LOCOS 为局域氧化区,POLY 为多晶硅覆盖区,CH为欧姆接触孔,GOX为栅氧,PSG为磷硅玻璃,N+、N-、P- 分别为N型高掺杂区、N 型低掺杂区、P 型低掺杂区。图1(a)中多晶覆盖区边缘呈圆弧形,其沟道呈放射状分布,具有比直线型排列沟道更大的宽度。

图1 200V/100A VDMOS 器件元胞结构示意图

摘要:分析了功率MOSFET 最大额定电流与导通电阻的关系,讨论了平面型中压大电流VDMOS器件设计中导通电阻、面积和开关损耗的折衷考虑,提出了圆弧形沟道布局以增大沟道宽度,以及栅氧下部分非沟道区域采用局域氧化技术以减小栅电容的方法,并据此设计了一种元胞结构。详细论述了器件制造过程中的关键工艺环节,包括栅氧化、光刻套准、多晶硅刻蚀、P 阱推进等。流水所得VDMOS 实测结果表明,该器件反向击穿特性良好,栅氧耐压达到本征击穿,阈值电压2.8V,导通电阻仅25m Ω,器件综合性能良

- 凌力尔特大功率多相同步升压型DC/DC控制器LTC3787(10-15)

- 电动自行车控制器MOSFET驱动电路的设计(11-18)

- 两种常见的MOSFET驱动电路设计(12-02)

- 集成MOSFET 的分立器件方案(01-30)

- 功率MOSFET的锂电池保护电路设计(04-18)

- 提升电源转换效率的自定时电压检测同步MOSFET控制方案(10-11)