集成晶体的可编程时钟可提供多种设计优势而无性能折衷

决支持多输出和可编程的巨大问题]

封装技术的突破避免了性能折衷

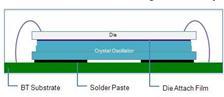

幸运的是,现在已经拥有了一个替代方案,不再需要在一个共封装、单一频率时钟发生器与独立的晶体外加一个可编程多输出器件之间进行选择。IDT公司的VersaClock5系列包括多款器件,其中集成式、共封装的晶体置于一个多输出时钟发生器硅片的下方,这些集成器件采用标准的塑料封装,与单独的时钟发生器IC具有相同的占位面积和0.9mm(标称)高度,如图3所示。

图3:IDT公司VersaClock5系列中的几款产品把时钟IC硅片放置于石英晶体顶部形成同一封装,从而以单一封装得到一个完整的多输出时钟源和发 生器,其尺寸并不比单独的时钟发生器更大。

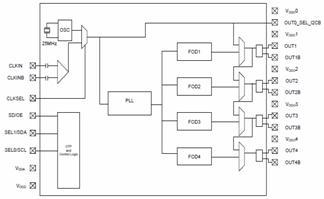

这里我们通过仔细分析VersaClock5系列中的一款共封装器件来展示其功能、性能、以及性能方面的不折衷。 4 × 4mm 5P49V5935器件能产生多达4个独立的输出频率(差分模式下频率高达350 MHz),每个输出都可配置为LVDS、LVPECL、HCSL或双LVCMOS,每个输出都具有单独可选输出电压(1.8V,2.5V和3.3V),见图4,其中四个输出都具有单独可编程输出使能、摆率控制和扩频功能。

图4:5P49V5935设有4个输出,每个都可以按照频率、输出类型和其他重要属性而独立配置。

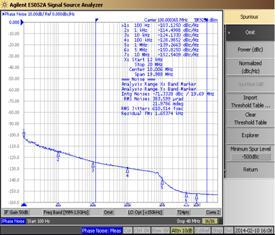

如图5所示,5P49V5935器件具有不到700fs RMS(均方根)的相位抖动,可满足诸如1G/10G以太网和PCI Express Gen 1,2,3等标准非常具有挑战性的要求,也可满足许多广泛使用的SoC和FPGA的时钟产生要求。由于该器件的内核电流消耗仅为30mA,不会消耗更高的功率。

图5: VersaClock5系列中5P49V5935的抖动性能表明,没有产生任何性能折衷:从12 kHz至20 MHz频率下,抖动低于700 fs,与采用外置晶体的标准解决方案相比旗鼓相当或者更优。

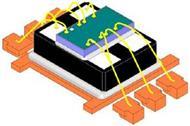

在把两个高频元件放置如此靠近时(即本例中的石英晶体和时钟IC),所担心的问题是由于两个元件之间微妙的相互作用而可能导致性能下降,如图6所示。在VersaClock5产品系列中的5P49V5935情况下,没有任何负面影响,其关键性能指标与两个器件方案相比旗鼓相当甚至更好。

图6:由于了先进的内部组装和封装创新,在采用5P49V5935时不会有性能或尺寸大小的折衷。

采用VersaClock5产品系列的一体化晶体IC能够减小电路板空间,当然也针对单一产品简化了BOM,而对于一系列的产品线更是如此。采用VersaClock5产品系列也有一些隐含的好处,但同样也很重要。像5P49V5935之类的集成元件可以保证晶体与时钟发生器配对工作时的性能表现,不再需要对电路和布局进行微调以便适应晶体的特定负载参数,这种一致性和在其它设计中的可重用性缩短了设计周期。

把时钟IC芯片置于晶体之上听起来像是一件非常容易实现的事情,但事实上不是这样,尤其是在要求不可影响性能时更加困难。IDT公司VersaClock 5产品系列的这些产品采用堆叠式、共封装设计,为工程师提供多输出、可编程时钟发生器,它虽然使用外部晶体,但却拥有一个不比单独的时钟IC更大的单一封装。这种组合式时钟源的技术指标已经"锁定",因此,不会由于布局、噪声或晶体的变化而出现意想不到的问题。它是一种技术上非常稳定可靠的解决方案,没有性能折衷,并具有出众的时钟性能指标、低功耗和小尺寸。

VersaClock5 石英晶体 MEMS振荡器 IDT 相关文章:

- 伺服系统在石英晶体切割设备上应用(05-02)

- 双口RAM在DSP与ICCD通信系统中的应用(02-09)

- 热仿真加速新产品上市(06-04)

- 如何确定嵌入式设计可接受的抖动水平(04-15)

- 如何提高芯片级封装集成电路的热性能(03-16)

- Android在TQ2440开发板上的移植(11-20)