集成晶体的可编程时钟可提供多种设计优势而无性能折衷

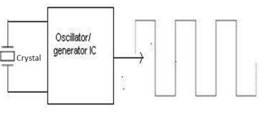

除了少数罕见的特例以外,几乎所有的电子系统都至少拥有一个时钟功能,这已经不是新闻。在大多数情况下,该时钟功能是通过采用石英晶体加上相关振荡器或时钟发生器集成电路实现,这种基本的实现方式可提供一个单一、固定频率输出,如图1所示。

图1:在一个基本的时钟产生方案中,采用一个石英晶体和一个振荡器/时钟发生器IC来提供所需的时序信号。

如果所需要的只是一个单一的时钟输出,时钟子系统的实施会非常简单。但对于当今复杂的电子产品,一个单一的时钟远远不够,多数产品都需要几个不同的时钟用于各种外部连接接口(如以太网、PCI、RapidIO和USB端口等等),另外也需要几个时钟用于内部功能(一个系统处理器以及专门的子系统)。

要提供所有这些彼此互不相关的时钟,显而易见的解决方案是采用多个晶体,每个晶体都有与其相关联的时钟发生器。这种途径技术上是可能的,但是没有任何吸引力,因为这种方案会导致出现许多问题,如需要更大的印刷电路板空间、电路板布局的挑战、复杂的材料清单(BOM)以及成本等等。结果是,除了科学仪器等一些非常特殊的情况,此时的时钟必须满足极端或独特的指标要求,上述方法并不可行。

人们更倾向于采用的更好解决方案是使用一个多路输出时钟发生器,由一个IC提供来源于单一晶体的多个彼此不相关的频率,如图2所示。这种方法克服了使用多对晶体和时钟IC产生的许多问题,因为该方案仅需要一个单一晶体和相关的时钟发生器,就可以为系统产生所有独立的时钟。

图2:一个典型的产品设计需要一个彼此不相关的时钟阵列,跨越范围广阔的频率和信号格式。这些可以通过采用单一晶体和多输出时钟发生器IC而轻松实现。

进一步讲,系统设计人员可受益于采用一个可编程时钟发生器。该发生器并不是产生固定的输出频率,用户可以根据一个产品的具体要求来把输出设置到他们需要的频率,或者在用户产品系列的多个产品中采用同样的时钟发生器IC。

使用单一的时钟发生器IC当然能够简化系统的BOM,对于设计师来说更有其他的好处。由于他们并不再需要其他元器件的数据表,并了解其正常工作所需的细节要求,如电源电压详情、布局准则、输出负载参数、各种公差等等,因而可以节省许多设计时间。除了最简单的集成电路,了解这些细节属于设计周期一个自然的组成部分,往往都在所难免的。在设计周期中,设计和物料清单中使用"我很陌生"的IC数量越少,产品面市的时间就越短。

然而,即使采用了可编程的多输出时钟发生器,外部晶体仍是一个大问题。首先,无论采用多小封装尺寸的晶体,它还是会占去不少在许多设计中都非常宝贵的电路板空间。此外,随着当今的时钟达到GHz水平,电路板上晶体和时钟发生器IC之间很短距离的布线可能产生潜在的噪声和EMI/RFI(电磁干扰/射频干扰)问题,造成附加的抖动、偏移(skew)和失真,从而降低时钟输出的性能。需要注意的是,即使晶体和时钟发生器本身都是"完美"的,但在目标负载处所看到的最终时钟性能会因PCB布局而受到影响。

最后,在采用不同的厂商提供晶体时,会出现由于生产过程不同导致出现的产品性能一致性问题。在晶体的指标中有许多二级细节差别,这些同样也会影响它们的性能和彼此互动,而且往往无法预判。因此,来自一个供应商的晶体也许可以正常工作,但是来自其他厂商表面上相同的晶体却可能存在"细微"的特性差别,使性能发生改变,这种问题可能会成为制造和生产测试中的重大难题。

共封装解决方案

解决由晶体和邻近的时钟发生器IC导致出现的问题的方法显而易见,至少在理论上是这样:把晶体和振荡器IC置于同一封装内,使其紧密靠近(或堆叠)振荡器IC。封装技术的最新进展使得共封装变得可行,并且被广泛应用于多IC设计,如采用一种半导体工艺制造的处理器与采用另一种工艺制造的存储器的整合封装。

显然,将时钟发生器IC硅片放置在晶体顶部可以节省印刷电路板空间。但是,这种集成技术以前只适用于单一频率的时钟发生器,不能体现出用一个集成式晶体和时钟发生器IC提供多个时钟的好处。换句话说,如果用以往的共封装技术解决问题很有局限性,这种局限性导致的问题比它试图解决的问题更大。

[注意,一些厂商正在提供基于MEMS技术的替代产品来取代晶体振荡器。通过采用基于MEMS的振荡器电路,可以得到一个体积更孝单芯片或双芯片共封装的时钟解决方案。总体来说,这些器件的性能对于某些应用已经足够,但不适合于所有应用,而且,只适用于单一频率时钟输出。因此,即使采用MEMS振荡器,依然不能解

VersaClock5 石英晶体 MEMS振荡器 IDT 相关文章:

- 伺服系统在石英晶体切割设备上应用(05-02)

- 双口RAM在DSP与ICCD通信系统中的应用(02-09)

- 热仿真加速新产品上市(06-04)

- 如何确定嵌入式设计可接受的抖动水平(04-15)

- 如何提高芯片级封装集成电路的热性能(03-16)

- Android在TQ2440开发板上的移植(11-20)