简述嵌入式逻辑分析仪在FPGA测试中的应用

3设计下载

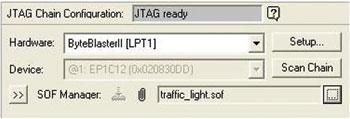

当设置完stp文件并编译综合后,软件将ELA IP嵌入设计里面,同设计一起下载到FPGA中。在器件列表中,逻辑分析仪会自动探测编程硬件,如果在保存设计前已经选好了FPGA中所使用的芯片,就会自动给出已经选好的器件,若没有选择,则需要在器件列表中选择。当器件连接成功,在SOF(SRAM Object File)管理器中选择需要下载的SOF文件,单击下载按钮即可将设计下载到FPGA中,如图4所示。

图4设计下载窗口

4在线调试

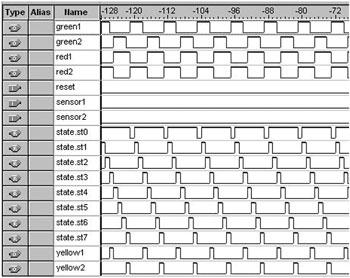

在线调试即利用JTAG接口将数据上传到调试软件中,根据实时运行的结果来对设计进行调试。本设计所实现的功能是在时钟信号的控制下,根据当前的状态决定下一个时钟周期的输出,即红灯、绿灯和黄灯的开启。

图5 SignalTap II数据窗的实时监测信号

设计中所得到的波形如图5所示,从图5中可以看出,对于第一组灯,在state.st3时,黄灯开启,绿灯及红灯都关闭,一个时钟周期后,跳转到state.st4,黄灯关闭,同时红灯开启;四个时钟周期后,跳转到state.st0,红灯关闭,同时绿灯开启,黄灯继续关闭;三个时钟周期后,再次跳转到state.st3,黄灯开启,绿灯关闭;一个时钟周期后,跳转到state.st4,黄灯关闭,红灯开启。对于第二组,其红绿灯的转换也是一样的不断循环,这样就实现了红绿黄灯的交替变化。

在线调试得到的波形与交通灯控制器设计中所要求的功能完全吻合,在上述调试过程中,嵌入式逻辑分析仪对内部的8个状态能够很好的监测,保证了设计的正确。

在调试过程中,用户可以很方便的开始或暂停ELA,对内部信号进行分析。如果需要修改设置,如采样深度或触发条件,只需停止运行ELA,完成修改后重新编译综合即可,缩短了调试时间。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)