数字化应用中的多核DSP

Turbo解码协处理器。其中维特比协处理器用於语音和低码率数据通道解码,支持500个8Kb/s码率的语音通道,并且可以对强制长度、码率和帧长度等解码参数进行编程。Turbo协处理器用於高码率数据通道的解码,支持35个384Kb/s码率的数据通道。

B、飞思卡尔MSC8126

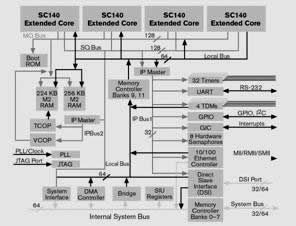

飞思卡尔半导体公司的MSC8126也是一个集成了协处理器的多核DSP。该DSP集成了4颗StarCore DSP核、一个Turbo协处理器、一个维特比协处理器、UART介面、4个TDM串列介面、32个通用定时器、乙太网介面

图9飞思卡尔MSC8126内部功能

该DSP在最先进的90nm工艺下生产,在400MHz主频下,其4个扩展内核可以达到最高每秒6400MMAC(百万次乘加操作)的性能。除了每个DSP核内包含228KB的M1存储器之外,片内还集成了476KB的共用M2存储器。支援可变长指令

是该DSP的另外一个特点。

4、DSP展望

Forward Concepts的Will Strauss表示∶DSP技术的演绎趋势是多重核心处理器。未来10年,全球DSP产品将向著高性能、低功耗、加强融合和拓展多种应用发展,DSP晶片将越来越多地渗透到各种电子产品当中,成为各种电子产品尤其是通信类电子产品的技术核心,将会越来越受到业界的青睐。

据TI预测,到2010年,DSP晶片的集成度将会增加11倍,在单个晶片内将能集成5亿苹晶体管。目前DSP的生产工艺已开始从0.35mm转向0.25mm、0.18mm,预计到2005年,DSP晶片的工艺将达到0.075mm的更高水准,届时,将能够在一块仅有拇指大小的单个晶片上集成8个DSP内核。

- 基于TMS320F2812的数字化三相变频电源的研制(01-15)

- 一种实用的嵌入式Web服务器设计(01-15)

- Fieldbus会话数字化-从模拟通讯到数字通讯转变(12-19)

- 现场总线技术在数字化电厂中的应用(12-19)

- 数字化仪表系统的现场总线技术特点(12-19)

- 数字化仪表系统的现场总线控制探析(12-19)