数字化应用中的多核DSP

领域的後起之秀,其高性能CT3616处理器内部集成了16个核与8个GPP(通用处理器)核,主频375MHz,能够进行16路MPEG4 SP@L3实时编码,最高性能达到96G MAC运算。可编程I/O是该处理器的另外一大特色,共有144个可编程的I/O引脚,允许用户自定义介面。该处理器集成的DDR DRAM介面可以挂接333MHz的DDR存储器。全晶片的功耗仅仅为4.5W,可以应用於音频/视频编码、多路监控、系统控制等领域。

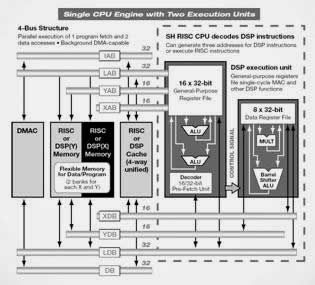

C、瑞萨半导体SuperH系列

瑞萨科技SuperH系列集成了32位元SH-2A CPU核心的DSP产品可用於工业、办公自动化和消费电子应用的设备控制。由於SH-2A CPU核心与SH-2保持指令的向上相容性,可提供更高的处理性能和ROM编码效率,可以满足市场对更高性能的需求。

图7 瑞萨科技SH-2A核心架构

其中,最近发布的带有片上闪存的SH7211F集成了可提供卓越实时控制能力的高性能SH-2A CPU核心,在160MHz运行条件下可以实现大约320 MIPS(每秒百万指令)的高处理性能。与SH-2 CPU核心相比,在同样的工作频率下其处理性能大约提高了1.5倍,与运行於80MHz最高工作频率的SH-2产品相比,性能大约提高了3倍。其指令集的向上相容性保证了可使用现有的程式,同时可以提高大约25%的ROM编码效率,并可减少存储程式的存储器容量。

SH-2A CPU核心在实时能力也有所改进。15个寄存器组专门用於CPU的中断,中断处理的反应周期已从SH-2的37个周期减少到SH-2A的6个周期。由於更高的工作频率和更短的反应周期,在160MHz工作条件下运行的SH-2A的程式开始反应时间的中断信号已减少到在80 MHz条件下运行的SH-2反应时间的大约1/12。这样,就可以在中断事件发生时,实现快速的程式切换,从而提供高质量的实时控制。

SH7211F还包括了适用於诸如AC伺服系统和变频器等强调实时控制能力的高档工业设备的各种外设功能。这些功能是具有3相PWM(脉冲宽度调制)输出能力的、8个12个位A/D转换器通道,以及2个8位D/A转换器通道变频设备使用的MTU2和MTU2S电机控制应用的理想选择。其通信功能包括有助於外围设备通信的I2C总线介面通道和具有16级FIFO的4通道串列通信介面。外部数据总线能够支持闪存ROM、SRAM、SDRAM、突发ROM、多工I/O,这些都可以通过总线状态控制器进行设置,使各种存储器能够进行直接连接而无须使用外部元件。

D、picoChip公司picoArray多重核心处理器

picoChip针对新一代无线系统的picoArray多重核心处理器阵列元件--PC202、PC203及PC205为高整合度、高效能、低成本之DSP。三款元件均内建约200个以上的处理器,提供超过100GIPs与25GMACs的运算效能,大幅领先旧有的单核心DSP。

图8 picoArray多重核心处理器阵列元件原理

其中,PC202与205亦内建一个性能强悍的ARM9处理器。所有新产品均采用标准C语言或组译语言撰写程式码,让客户能利用其开发完整的软体无线电系统,此外并针对WiMAX(16d与16e)以及WCDMA(包括HSDPA,并能升级至HSUPA)提供完整的参考设计方案。

PC202内建198个数位讯号处理器,以及一个负责控制与MAC功能的ARM 926EJ-S处理器,以锁定各种追求低成本的应用,例如WiMAX客户端系统与存取设备、以及WCDMA毫微微蜂巢式(家用基地台)设备。

PC203内含248个处理器,系专为基地台(BS)应用所设计,能协助业者开发出支援各种热门无线通讯协定的产品,例如WiMAX与HSDPA/HSUPA,包括支援如MIMO与波束成型等先进演算法,C203尚能搭配外部控制处理器或网路处理器,开发出大型基地台产品。

此三款晶片均内建加密引擎,针对高速傅立叶转换/反向高速傅立叶转换、Viterbi、以及涡轮高速解码器(包括符合16e规格的CTC),此功能完全整合至picoChip的互连架构与开发环境,让业者能轻易进行编程、整合、以及验证。

另外,每个处理器均为功能完备的DSP,内含16x16乘数器与40位元累加器、内部指令与资料记忆体,采用一套改良式三路超长指令字元(LIW)架构,此意味著处理器可执行乘数-累加(MAC)指令,每个周期最多可处理三个其他指令。PC203与PC205内含的248个处理器,运作时脉达160MHz,即使在针对如Turbo与Viterbi解码与加密作业时,亦能达到约160 GIPS的无线通讯加速效能。

(3)DSP核+协处理器

这类DSP一般针对某一类应用集成专用的协处理器,从而对DSP实现演算法加速。TI的研究表明,对於像MPEG4编解码这样的任务,使用协处理器可以降低50%的DSP负荷,从而平衡系统功耗。

该DSP除了包含一个功能强大的C64x DSP核之外,还集成了一个维特比协处理器(VCP)和一个

- 基于TMS320F2812的数字化三相变频电源的研制(01-15)

- 一种实用的嵌入式Web服务器设计(01-15)

- Fieldbus会话数字化-从模拟通讯到数字通讯转变(12-19)

- 现场总线技术在数字化电厂中的应用(12-19)

- 数字化仪表系统的现场总线技术特点(12-19)

- 数字化仪表系统的现场总线控制探析(12-19)