基于DSP的液晶显示器接口设计及控制实现

图中电阻大小均为2kΩ。SLK,SLA分别为LED背光源正负极;Vdd,Vss分别为LCD的电源和地;CSl,CS2为LCD片选信号,当CSl为低,CS2为高时,LCM320240处于就绪状态,随时可接受指令。LCM320240的DB0-DB7与DSP的IOPB0-IOPB7相连,实现数据传送;IOPE0与RS相连,当RS为高时,DSP存取指令寄存器,而当RS为低时,DSP存取资料寄存器。IOPEI与WR(R/W)相连,当LCM320240为6800系列时序时,此引脚为读取/写入信号,高电平时表示读取的动作,低电平时表示写入的动作;I0PE2与RD(E)相连,当为6800时序时,EN为使能信号,高电平有效;IOPE5设置为输入方式,与BUSY相连,当BUSY引脚为高电平时,控制器无法被存取,DSP必须在对控制器做存取前确定该引脚为低电平才可对LCM320240进行操作;I0PE6设置为输入方式,与INT相连,此引脚可设成高或低电平触发,当光标Segment位址寄存器(CPXR)与Segment中断位址寄存器(INTX)值相同,或光标Common位址寄存器(CPYR)与Common中断位址寄存器(INTY)值相同时,发生中断,触发该引脚;IOPE7与RST相连,当IOPE7设置为低电平,且持续时间不小于LCM320240规定的最小时间100ms时,LCM320240复位;VOUT为液晶模块的负电压输出,LCDV0为LCD的工作电压(调节LCDVo的值可以调节显示对比度),通过调节可变电位器,可以调节液晶屏的显示对比度。

5 软件控制实现

DSP可以采用汇编语言或C语言作为开发语言进行程序设计,但考虑到系统的可移植性和软件的可读性,本文以C语言作为开发语言,介绍DSP与LCM320240之间控制程序的实现。

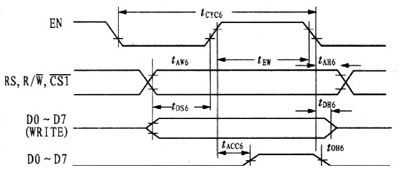

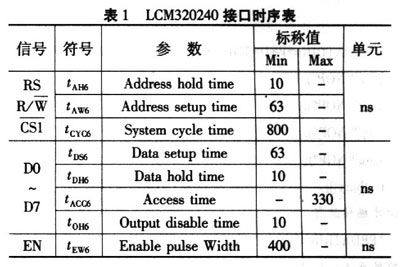

首先解决TMS320LF2407与LCM320240之间的时序匹配。时序匹配是DSP控制LCM320240最关键也是最基本的问题,其本质就是如何编写控制程序对LCM320240的指令寄存器和资料寄存器进行读写操作。LCM320240所采用的6800时序图如图2所示。LCM320240接口时序如表1所示。

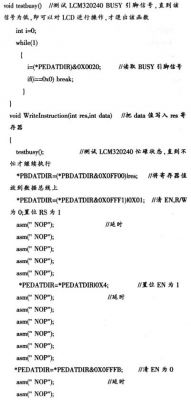

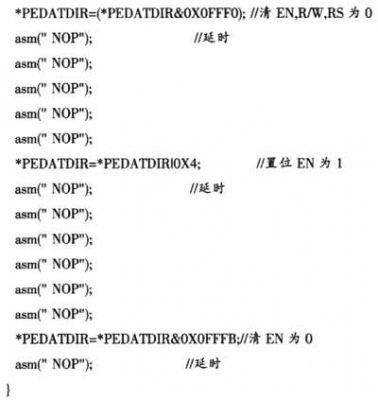

根据LCM320240的时序图和时序表便可以编写与时序匹配的DSP控制程序。以写指令寄存器和写资料寄存器程序为例,程序源代码如下:

其次,进行系统初始化设置,包括DSP和LCD的初始化。DSP初始化主要完成DSP与LCD相连的I/O口的功能配置;LCD的初始化主要完成对LCD工作方式和显示模式的设置,需要特别指出:在LCD初始化中应对LCD进行一次复位操作,为后续对LCD进行操作程序做好准备(源代码略)。

最后,在完成系统初始化后,根据实际系统的需要,通过调用已经编译好的时序匹配的LCM320240控制程序来完成对实际系统程序的编写。

6 结束语

文中介绍的DSP控制LCM320240的软、硬件实现方法已在便携式检测仪中得到应用,运行效果良好。同时,本文所用程序采用C语言编写,具有较高的可移植性,对其他类型的DSP与LCD之间的软、硬件实现具有一定的参考价值。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)