一种基于DSP的并行信号处理系统的设计

,恒虚警检测子模块由4个单元构成,M/N检测汇总子模块为1个单元,并行子模块之间由高速通信口相连,每对通信口间数据传输速率可达40 Mb/s。所有DSP都有通信口通过电路板插座连接到外部,利用数据流格式和相应的软件配置在邻近电路板间建立数据通路,这样减少了电路板间信号耦合。

4.2软件处理及实现分析

程序部分完成:CFAR、幅相计算、M/N检测等功能,需要5片DSP。

整个距离分4段,分别在4片DSP中进行CFAR、幅相计算等处理。段间有重叠,以保证每一段CFAR的左右单元平均可以独立进行。最后将4段的结果在下一片DSP进行合并、M/N检测,把目标信息后送。

(1)CFAR,幅相计算

杂波图恒虚警检测的主要功能是利用相应方位的杂波图输出作为门限,对零号滤波器各距离单元进行检测。其他滤波器输出采用单元平均CFAR处理方法对每个距离单元进行检测,同一个距离门的N-1个多卜勒通道检测结果选大作为CFAR检测结果,并与杂波图检测输出经或门后作为最终检测结果。检测结果有目标输出时,保留其幅值、相位信息。

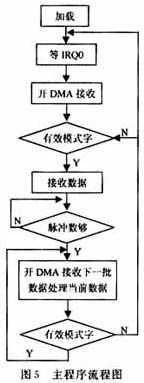

程序流程分别从LINKX接收各自段的数据,先对数据作CFAR处理,检测到目标后,保存对应距离/多普勒单元信息,等到所有数据都处理完后,把结果通过LINKX送往下一级,主程序流程如图5所示。

其中IRQ0是相干处理周期的起始信号,模式字的有效性通过校验码实现,高速通信口LINKX工作在DMA方式。

输入与输出的数据格式输入数据先是4个字的模式,接着是实、虚部交替的复数,个数同模式有关,每个复数对应一个距离/多普勒单元。CFAR检测结果格式,先是以4个字的模式,逐个字地检测到目标的个数,接着是各目标单元信息。

由于这一级在最不利的32点FFT情况下存储量大约为90 k个复数,所以DSP芯片选取了内存较大的ADSP21060。

(2)汇总与M/N检测

这一级的汇总任务是把4段的CFAR检测结果合并到一起,只要把各段中各个目标单元依据距离门的位置加以修整,然后搬到另一处缓冲区即可。这时目标信息排列的顺序是按距离门号依次递增的,先搬整个距离段上距离门号最小的第1段,再搬第2,3,4段。

M/N检测在相干处理周期间进行,其准则是相邻3个相干处理周期内至少有2次在同一个距离门上检测到目标,确认为相对应距离单元上有目标输出,这时保留相应单元上最新的幅值作为检测结果。

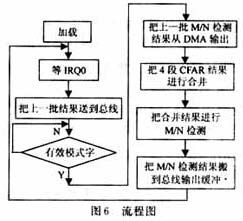

程序流程如图6所示。分别从LINK2,LINK3,LINK1,LINK5接收4个距离段上的检测结果,把4段的结果合并在一起,形成整个距离段完整的结果。然后和以前2次检测的结果进行M/N检测,最后把M/N检测的结果通过LINK0发往接口板。

四段的输入数据格式相同先是4个字的模式,逐个字地检测到目标的个数,接着是各目标单元信息。存储量不大,选取了内存较小的ADSP21062。

4.3 运算量、内存、通讯资源占用情况

在CFAR检测中,包括零多卜勒通道各距离门利用相应波位的杂波图作为门限进行检测,剩余滤波器在距离上的单元平均恒虚警检测。其运算量主要集中在单元平均恒虚警中,这里除了第1个距离单元两端各项需经L个数据平均外,在第2个距离门后的其余距离单元检测时,前后各L个数平均只需加上1个新移进的值,减去移出的值即可,这样对每个距离门检测来说只需约8条指令。汇总部分运算量不大。由于汇总要处理前一级众多DSP芯片数据,因此此处数据通信充分利用互连网络的各通讯支路进行数据转发,其前一级运算部分在缓存及时间上要给此部分留有一定余量。

CFAR一级在32点MTD模式下存储压力较大,因此采取了以下措施:输入/输出以及中间结果都是短字定点格式,在开始CFAR检测前要先转换成长字的浮点格式进行各种运算,最后把CFAR结果经过定浮点转换作为16 B定点格式保存下来,其余部分的运算也需要先把CFAR结果转换成32 B浮点格式,不过是在所调用的子程序内部完成的。作为运算的中间结果,目标单元幅值的存储使用了循环寻址方式,因为一批数据在一边被进行处理的同时一边会被新来的数据覆盖掉,这一过程是以距离门的顺序进行的,而CFAR检测也是沿着距离门滑动的,在对第18号距离门检测时,第0号距离门的数据就没有任何用途了,这样就可以把第18号距离门的幅值存到第0号距离门的位置。同样地第19号距离门的幅值也可以存到第1号距离门的位置,从而构成了循环寻址存储方式。其他一些中间结果也采用了这种存储方式,有效地节省了内存资源。

CFAR一级包括单元平均恒虚警检测和幅相计算2部分,运算量主要集中在前一部分,占90%左右,到后面的数据量已经大大减少了。汇总一级的运算量主要集中在M/N检测部分,但总的运算量不大。

5 结语

本文讨论

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)