һ�ֻ���DSP�IJ����źŴ���ϵͳ�����

Ϊ��������Ԫ�ṩ���ݽ�����ͨ·�������������ͺͿ��Ƶ����źŵĴ��ݡ�������Ԫ֮�������ṹ���¿ɷֳ�2�ࣺ

����(1)�������ߣ�������������ϵͳ����Ϊ�����ʽ����ϵͳ��

����(2)������Ԫ�и��Զ��������ݴ�������ͨ��ͨ�ſ������ķֲ�ʽ����ϵͳ���ֳ������ʽϵͳ�������ʽ�Ĺ�������ϵͳ�ڴ�����Ԫ�������ٵ�����£�������������ͨ�Ŷ��ܻ�ýϸߵļ��ٱȡ���������Ԫ�����ܶ�ʱ���������߽����Ƶ�������߳�ͻ�͵ȴ������ҹ������߽ṹ�Ŀ������Ժ�����Բ����ֲ�ʽϵͳ�������ڴ��ģ���д���ϵͳ�����ع��������ݴ�������Զ����ֲ�ʽϵͳ��

����ͨ�ò���DSP��ͨ�ſ��ٶ���30~60 MHz����Ϊ�ڴ�����Ԫ��Ŀ�ܶ�Ĵ��ģ���д������÷ֲ�ʽϵͳ��ƴ�����������TMS320C40��ADSP21060�ṩ�Ķ��6������ͨ�ſڵ���ͨ����������ָ���ٶȻ�ƽ�����������൱����ͬʱTMS320C40��ADSP21060���ṩ�˹����������ߵĽӿڣ�TMS320C40��2���������ߣ�����һ�������ں�����TMS320C40�������ݣ���ADSP21060��Ƭ�ھ��й��������ٲ��������������������ⲿ���Ƶ�·������£���������6��ADSP21060ֱ��������

�������Ϸ����������ֲ�ʽ����ϵͳ���ʺ��ڴ��ģ����ϵͳ������������ʽϵͳ��С��ģ�IJ��д������Ͽ��Եõ��ϸߵ����ܡ���ADSP21060Ϊ������������ԪС��5ʱ��������ϵͳ��Ч�ʽϸߣ���֮���ֲ�ʽ����ϵͳ�����á�

����3.3 �����㷨�����������������

���������㷨�ĺû���Ҫ���䲢�жȸߵ��������������㷨�Ͳ��г������Ƹ��Ӷ�Զ���ڴ�ͳ�Ĵ����㷨�ʹ��г�����ƣ�������������ڴ������ṹ�����еIJ����㷨Զ�������㲢�д�������Ҫ������Ŀǰ��ȱ��һ����Ч�IJ��п���ϵͳ�Ͳ���������ԣ��������״��źŴ�����һ������˵���źŴ�����������ͻ�������ȷ���ģ������С������ߵ���Ʒ�Χ���Ӷ��������˳�����Ƶ��Ѷȡ�

�����������������IJ���DSP��Ϊ������Ԫ���ɵ��źŴ�����������ȫ�ɱ�̺����������صģ�������Ҫ���ԶԲ�ͬ������ģ�����½��й��ܶ��塣�㷨�����Ա�ģ������DSP��RAM��ROM�У���������Ԫ�Ĺ��ܸı�ʱ���ɵ�����Ӧ������ģ�顣

�����������͵������Dz��д���ϵͳ��Ƶ�һ�����⣬��������ʵ�õ������Զ����䷽��������������������ijɱ���̫�ߡ������״��źŴ������е��ص㣬���Խ��䶨��ɴ����������������ģ�飬ÿ��ģ����������������IJ�ͬ�����������������ʱ�䡢����ͨ��ʱ�䡢����ͨ��·��������ͬ��

��������������ȫ�����ķ�ʽ�ǽ����������е�ȫ�����ݷָ��һ����С�����ݰ�����ÿ�����ݰ��У�����ʵ�����ݻ�������������Ϣ�����ݰ����ȡ�������ʽ������������У���롣������ʽ�к����㹻�Ĵ�����Ϣ������ָʾDSP����ģ����δ����˰����ݣ���ѡ��������˲���MTI��CFAR�ȡ�����������Ϣ��ϸ�ظ����˴˰����ݵ��ص㣬������������ֹ�š������պš�ͨ���ŵȡ�DSP���յ�һ�����ݰ�������˰����ݵĴ���������������ݰ��Ƕ����ģ������������д���������ȴ����������ݵ������������DSPת������

����4 ϵͳ��ʵ��

�������ȹ���һ�µ�Ԫƽ�����龯�������������������루���120 km,7 MHz�����ʣ�������Ϊ5.6 k��������1ƬADSP2106X������Ҫ��ʱ���Լ��3.6 ms��������ɴ�������Ϊ1 ms����������ھ����Ϸֳ�4�Σ��ֱ���4ƬADSP2106X��������������0.1 ms�Ŀ���ʱ�䡣����Ϊ��ÿƬDSP�������ݷ��㣬��Ҫÿ�δ������������˶μ�Ҫ���ص����Ա�֤ÿһ��CFAR�����ҵ�Ԫƽ�����Զ������С�

������1�����ں��龯���Ĵ�����˵��ֻ��2�ֹ�����ʽ��MTI��MTD���ֱ��Ӧ��Ԫƽ�����龯���Ͷ�ά���龯��⡣

������2��ϵͳ�ڸ����־�������������ʽ���������ݰ��ĸ�ʽΪ������4���ֵ�ģʽ�����֣�Ȼ����ʵ�����ݡ�ÿһ�ֹ�����ʽ����Ӧ������ÿһ���ݰ�ǰ���ģʽ�����ָ�������Ӧ��ģʽ�������еĹ�����ʽ�������ȸ����ò��֣��������������㵥Ԫ�ж�����н��ͣ��Ա�ת����Ӧ���ӳ���

������3��ϵͳ��ʼ����ʽ�����֣�һ����EPROM���ط�ʽ���˷�ʽ������������ϵͳ���Ի�̶��״﹤����ʽ���ѿ���������С���һ�ּ��ط�ʽ����ͨ��������ӿ���Link�ڼ��ط�ʽ���м��ء�Ϊ��ʹ��ʱ�����״��źŴ�����ʽ�����ü�������ط�ʽ��

����4.1 ϵͳӲ��

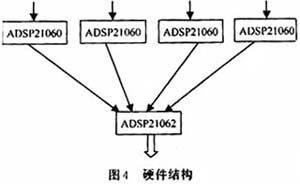

���������������ͺ��龯�������Ĵ洢�������Ƴ��豸��Ϊ5ƬDSP����ͼ4��ʾ��

�����״��źŴ�����ˮ���е��ص㣬�����������̽�����ϵͳ���ֳ����ɹ��ܿ飬��������÷ֲ�ʽ���д���ϵͳ���ֲ�ʽ���д���ϵͳ�ɱ��IJ�����ģ�鹹��

- �ڲ���FPGA���DSPϵͳ�з������Ҫ�� (06-21)

- ���� DSP Builder��FIR�˲����������ʵ��(06-21)

- ���������ý��Ƭ��ϵͳ�ļܹ���Linux��������(06-02)

- FPGA��DSP���ܽ���(06-16)

- ��CPLDʵ��DSP��PLX9054֮�������(07-23)

- DSP+FPGA�ṹ���״�ģ��ϵͳ�е�Ӧ��(01-02)