用单片机实现DSP在线调试的一种方法

通常情况下,进行DSP系统开发调试时,都要配备一片SRAM芯片作为片外程序RAM。调试时,使用相应的仿真板将程序下载到SRAM中,这样DSP系统通过运行SRAM中的程序代码来实现相应的操作。

可以看到,DSP系统调试时,关键是要将程序下载到SRAM中,因此如果能将程序代码通过单片机写入SRAM中,则同样可以完成对DSP系统的调试。下面具体介绍在不使用仿真板的情况下,如何运用单片机AT89S5l对DSP芯片TMS320LF2407进行在线调试。

1 硬件设计

1.1 TMS320LF2407在线调试的实现过程

完成DSP系统的调试,首先要将程序的源代码写入片外SRAM中。此时,单片机与SRAM组成一个系统,单片机可将分离出来的DSP程序代码写入SRAM中。完成这一操作后,切断单片机与SRAM的联系,使DSP与SRAM组成一个独立的系统,并将LF2407配置为微处理方式,即MP/MC引脚置为高电平。这样DSP系统开始工作,LF2407从外部SRAM的0000H单元处开始执行程序代码。当修改DSP的程序时,只需修改单片机中相应的代码区,然后重新写入SRAM中即可。单片机的ISP功能能非常方便的完成这一过程,实现DSP系统的在线调试。

1.2 硬件实现

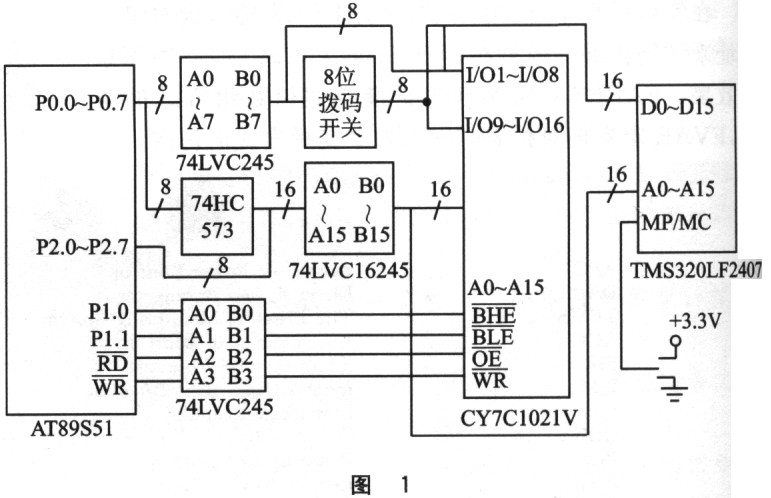

单片机选用AT89S5l,该芯片具有在系统编程功能,能通过并口下载线十分方便地修改和下载程序。TMS320LF2407的片外程序RAM选用64K×16位的SRAM芯片CY7C102lV,该芯片的BHE和BLE引脚分别用来使能SRAM的高8位和低8位。硬件框图如图l所示。

由于89S51是5V供电,而CY7C102lV是3.3V供电,因此要进行5V和3.3V电平的转换。图1中,单片机端的地址线和控制线分别通过74LVCl6245和74LVC245将5V电子转换为3.3V电平。数据线的电平转换建议采用74LVC245,该芯片采用5V和3.3V双电源供电,它可以将数据线上的5V和3.3V电平相互转换,可实现单片机读、写RAM中的数据。

读出的数据可以通过串口发送到计算机上,这样可以检验写入SRAM中的代码是否正确。89S5l为8位单片机,而CY7Cl02lV和DSP数据位都为16位,所以代码的写入要分两次写入,先写低8位,再写高8位。高8位数据线和低8位数据线之间可以加一个8位的拨码开关,当向SRAM中写数据时合上开关,而当要运行DSP时则必须将拨码开关断开。当代码正确写入SRAM后,将DSP的MP/MC引脚跳至高电平,选择MP方式运行片外程序RAM复位后,即可以使DSP运行。设计中一定要注意以下情况:由于MCU-SRAM和DSP-SRAM两个系统的数据线和地址线存在共用的情况,所以当一个系统在运行时,数据线和地址线不能受到另一芯片相关引脚状态的影响,否则这一系统将无法正常运行。因此,一定要注意控制好各个芯片的片选信号,以保证两个系统分别运行时地址线和数据线不相互影响。

2 软件设计

TI公司的CC’C2000编译后生成的*.out文件为通用对象文件格式(coft),该格式是一种结构性文件格式,而单片机的烧入程序必须为bex文件格式,所以要将*.out文件转化为hex文件格式才能烧人单片机中。转换步骤如下。

①生成*.out形式的公用目标文件(coff)。当在TI公司的集成开发环境CC’C2000下进行程序开发时,都会经过编译和链接,最后生成*.out文件。

②对*.out文件进行提取,从中筛选出对最后装载有用的代码和地址信息。

第一步所产生的*.out文件由于是coff格式的文件,其可重定位特性使得用户可以对程序在允许的地址范围内灵活地安排。正因为如此,*.out文件还不是完全的可执行代码,它里面包含有一些关于程序中各个段的诸如起始地址、段长度这样的辅助信息,如果把这些信息连同程序代码都装入DSP内部,程序是不会被正常执行的。这时必须要对*.out进行辅助信息与可执行代码的提取与分离,这个任务要靠专门的程序完成。这里采用TI公司提供的程序,程序的名称是:coff_both.exe。它可以在TI的网站上免费下载。

利用该程序将*.out文件进行操作,最后生成所需的*.out.c文件。具体操作是把Coff_both.exe和exam-pie.out文件放在同一目录下,在DOS命令提示符下键入:Coff_both-out example.out,这时就会生成example.out.c格式的文件。该文件的形式见如下。

sectlon=,vectors

src_addr=0x0

length=0x6(6)

dest_addr_0x0

space=0

0x7980,Ox0150,0x7980,0xol50,

0x7980,0x0150,

checksum=0x78D0

seCtlon=.text

src_addr=0x0

length=0xl3(19)

dest_addr=0x150

space=0

0xBE4l,0xBE46,0xBE42,0xBE44,

0xBCEO,0xAE18,0x83FE,0xAE29,

Ox00E8,oxBCE1,0xAEl0,0x0000,

0xAE1

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)