非规则LDPC码译码改进算法及其DSP实现

代译码算法和优化设计

文指出,在BSC信道下,S-SP算法可以有效降低迭代译码次数。本文研究了该算法在AWGN信道下的特点,发现该算法虽可以降低迭代译码次数,但是存在误码平台较高的缺点。后面将利用仿真结果说明这一特点。

本文将S-SP算法与修正最小和算法(MMS)结合,提出了改进算法,将外信息的更新采用串行更新策略,校验节点的计算采用修正最小和算法,称为串行修正最小和算法(S-MMS)。该算法解决了S-SP算法的误码平台较高的问题,译码门限和标准的SP算法相比,性能损失很小。

提出的串行修正最小和算法(S-MMS),其迭代译码步骤2修改如下。

设定固定的迭代次数K,对校验节点m,依次取1,2,3,…,M,进行下面的2个步骤。

1)变量节点的运算(只计算和校验节点m相连的变量节点)。

其中:r=│N(m)│表示集合N(m)中的元素个数,即非规则码的校验节点m的阶数;βr为非规则码不同阶校验节点的偏移因子;sgn()为符号函数。

最优的偏移因子βr值,可以采用密度演化或者计算机仿真的方法得到。

本算法变量节点的运算只包括求和运算,校验节点只包括最大、最小和减法操作,与SP算法的校验节点运算的非线性函数ln(tanh())相比,量化噪声对其影响小。本文针对定点DSP芯片特点,信道观测值和迭代译码中的外信息,都采用16 b的量化精度,有利于优化指令并行度,并可以降低存储器读取、存储延时。

3 算法性能仿真测试

为验证本文算法的有效性,结合非规则LDPC码对算法的性能进行了计算机仿真,并利用TI公司的定点DSP对其性能进行了测试。

仿真采用的非规则LDPC码的码长为4.096kb,码率为1/2,变量节点和校验节点的度分布分别为λ(x)=0.27x+0.25x2+0.01x3+0.47x9和ρ(x)=0.47_x6+0.53x7。

据ρ(x)可知,非规则LDPC码校验节点的阶数为7和8,通过计算机仿真得到的最优偏移因子分别为β7=0.45,β8=O.60。

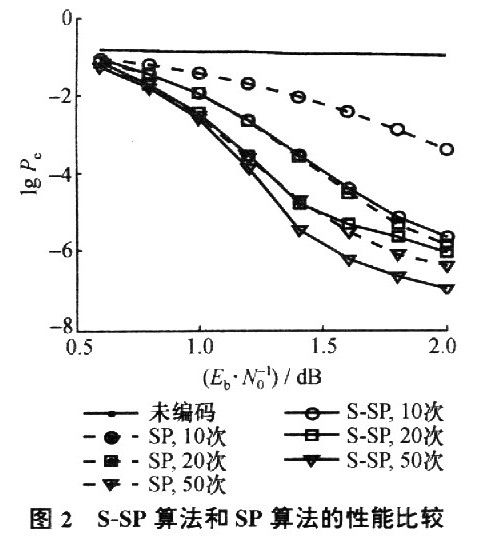

图2给出了不同迭代次数下S-SP译码算法和SP算法的性能比较。可以看出,在AWGN信道下,S-SP算法仍可以有效地降低迭代译码次数,或者说在相同的有限迭代译码次数下,尤其是迭代次数为10次和20次时,性能有明显改善;但是,S-SP算法的缺点是有较高的误码平台。

图3给出了不同迭代次数下,S-MMS算法和SP算法的性能比较。可以看出,S-MMS算法误码平台降低,译码门限略高于SP算法,在迭代次数较小时,性能仍有明显改善。当迭代次数为20,Eb/No较小时,S-MMS算法与SP算法相比性能略有恶化,但Eb/No较大时,性能有明显改善,且误码平台降低,例如误比特率Pe为10-5时,信噪比改善约0.1 dB。在误码率10-6时,信噪比改善约0.25 dB。当迭代次数为50,Eb/No较小时,译码门限恶化约0.15 dB,Eb/No较大时,性能仍有所改善,误码平台降低。

综合比较图2和图3,S-MMS算法和S-SP算法相比,Eb/No较小时,译码门限恶化约为0.1~0.2 dB,Eb/No较大时,例如在误比特率Pe为10-6时,性能仍有所改善。考虑到一般通信系统要求译码后的误码率低于10-5,S-MMS算法在Eb/No较小时的性能恶化对其应用影响不大,适合实际应用。

图4给出了不同迭代次数下,利用TI公司的DSP芯片TMS320C6416T实现的采用量化SMMS算法的译码器的仿真测试性能和未量化S-MMS算法的比较。可以看出,定点DSP芯片上实现的S-MMS算法和未量化的算法性能几乎完全一致,进一步说明了本算法利用DSP芯片实现的有效性。DSP芯片实现的译码器的具体性能见表1。

文中用DSP实现的LDPC码译码器采用的码长为10.228 kb,码率为1/2,在误码率10-5时,信噪比为1.65 dB。本文设计的译码器采用的LDPC码的码长为4.096 kb,码率也为1/2,若采用50次迭代,在误码率10-5时,信噪比为1.55 dB;因此,本文实现的译码器的纠错性能优于文中设计的译码器。另一方面,本文译码器设计使用C语言实现,指令级的优化可进一步提高工作速率。

4 结 论

本文提出了一种适合数字信号处理器(DSP)实现的低复杂度、低误码平台的译码算法。该算法校验节点运算采用MMS算法,节点间的外信息更新采用串行方式,既保持了S-SP算法有限迭代次数下译码门限低的优点,又利用MMS算法的优点降低了误码平台和实现复杂度,克服了S-SP算法的复杂度高、误码平台高的明显缺点,获得了较好的性能折衷,很好地适应了DSP芯片指令串行执行的特点。

- 一种基于FPGA的QC_LDPC码的译码器设计(05-13)

- T-MMB系统中LDPC码译码器的FPGA设计与实现(06-26)

- 水声OFDM系统中卷积码译码设计及其DSP实现(04-11)

- 基于51单片机的编码译码显示实验电路设计(11-12)

- 用BP神经网络及其改进算法改善传(02-11)