嵌入式系统的除错策略

工具领域多个供应商的经验基础上,实现片上除错功能与介面的标准化。由于该论坛的多个供应商已经为片上除错提供了专有产品,因此基本的片上除错要求已经足以轻鬆地达到 Nexus 的符合性。好处是 Nexus 跟踪介面的标准化,例如跟踪功能、信号、消息协定和应用编程介面(application-programming interface,API)。同时,标准化还为供应商的定制化提供充分的空间。Nexus 标准最初是针对汽车应用的,现已快速扩充到无线与网路市常

多核心除错

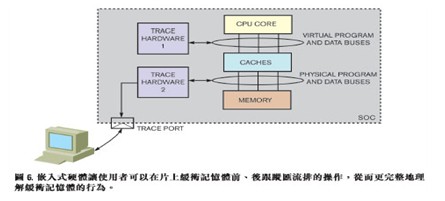

缓衡记忆体能提供高性能,但却难以除错,因为它们将 CPU 的执行情况与外部记忆体匯流排隐藏起来,并且难以了解到核心与 DMA 或加速硬体之间的一致性。嵌入式跟踪硬体有助于解决这个问题,因为被跟踪的匯流排通常是虚拟的(在缓衡记忆体以前),而非实体的。跟踪缓衝记忆体前、后的匯流排也非常有助于更完整地了解缓衡记忆体的行为(图 6)。

两个跟踪结果的比较,能够提供快取失败(cache miss)的良好指示,此时缓衡记忆体造成对实体匯流排的存取。这种方法有助于减少快取失败,并提高软体的性能。另一种方法是增加嵌入式的缓衡记忆体除错硬体,在除错模式下读取缓衡记忆体内容,或写入缓衡记忆体。这种方法通常采用缓衡记忆体除错暂存器形式,并透过软体或 JTAG 埠存取。使用者使用除错器可以暂停程式的执行,并检查缓衡记忆体的内容。使用者可以用这个资讯解决各种缓衡记忆体清除问题,如无效、同步或溢出。

现代 SoC 经常在一颗晶片内整合多个处理器,用传统的除错硬体难以对多个核心之间的互通性进行除错。有一种最新出现的除错技术叫交叉触发(Cross-triggering),它成为对复杂多核心 SoC 除错的常用方法(参考文献 8)。该方法的原理是将一个核心域的事件转换到其他核心域或相同核心域的产生触发器(generate trigger)上。典型事件是进入除错模式、发生中断、出现观察点,以及出现中断点。输入触发器一般是除错要求。触发器产生一个除错要求、一个中断,或一个 SoC 垫(SOC pad)的突波杂讯(glitch)。它们都可以啟动或停止处理器上的跟踪。触发器的组合将所有弹性留给了最终使用者,使他们能够设计出复杂的除错序列。可以在 Core B 到达某个程式位址时,用交叉触发器啟动 Core A 上的一个跟踪,或当 Core A 进入除错时,停止 Core B 的活动。

随着对 SoC 尺寸压力不断地增加,低成本除错可能成为嵌入式系统架构的圣杯。但是必须牢记一件重要的事:永远不要在系统的除错能力方面作出妥协。如果不能预先处理好系统的所有臭虫,那么以后就无法获得更大发现问题的机会。在减少嵌入式除错硬体上所节省的成本,其代价可能是在专案后期付出更高昂的软体除错成本。另外还应记得,除错与安全两种要求是相互矛盾的。很多制造商现在交付产品时只是简单地关掉除错功能来防止骇客的攻击。这种做法是不明智的。你永远不可能预期会在现场遇到什么问题。比较好的做法是采用各种安全方式防止进入除错部分,如用密钥或熔丝(fuse),这样才不会危及你的除错功能。

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)

- 嵌入式系统实时性的问题(06-21)

- 嵌入式实时系统中的优先级反转问题(06-10)

- 嵌入式Linux系统中MMC卡驱动管理技术研究(06-10)

- FPGA的DSP性能揭秘(06-16)