嵌入式系统的除错策略

除错电路板上的处理器。一个运行并模拟除错器功能的主机控制这个 ICE 盒。ICE 的主要局限性之一是它的价格昂贵。另外,虽然这个方法很适合简单的处理器,但现代 SoC 有更高的复杂性、整合度和频率,因此 IC 供应商难以为现代处理器提供 ICE 版本。

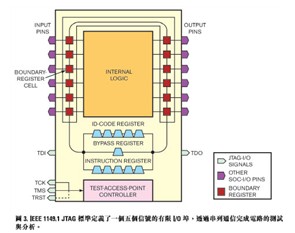

一些欧洲公司在1985 年成立了联合测试活动组(Joint Test Action Group,JTAG),这个联盟尝试要解决测试半导体 IC 的各种问题。它们为 IC 的边界扫描测试建立了 IEEE 1149.1 标准,并在 1990 年公布了此一标准(参考文献 5 和 图 3)。

JTAG 标准定义了一个有限的 I/O JTAG 埠,有多达五个信号,透过串列通信完成电路的测试与分析:测试时鐘(test clock,TCK)、测试模式选择(test-mode select,TMS)、可选的测试重定(test reset, TRST)、测试资料登录(test-data in ,TDI)和 测试资料输出(test-data out,TDO)。

IEEE 将 JTAG 硬体建立在一个 16 态的有限状态(finite-state)机上,并由 TMS 信号控制。TCK的上升沿时鐘(rising- edge clock)擷取到此一 TMS 信号。资料资讯在TDI 垫(TDI pad)移入,并在TDO 垫移出。最后用 TRST 来对设计重新设定。IC 的每个垫都可以增加扫描暂存器,并将它们内部连接起来构成一个边界扫描链。可以透过 TDI/TDO 和 JTAG 命令将此链移入和移出,以测试电路板上的外部连接,测试 IC 内部的逻辑连接,擷取 IC 垫的值,并将 JTAG 置于旁路模式。JTAG 提供了低成本的製造测试功能,并成为最常用的测试方法。但是,由于它有易于使用、高可用性和低成本实现的特点,设计者经常会把 JTAG 当作除错埠,以存取片上的除错资源(参考文献 6)。

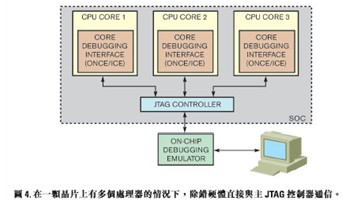

JTAG 是除错通信的传输层,位于运行在主机上的除错器与嵌入式处理器除错资源之间。命令被移入命令暂存器,以存取除错中的硬体 IP。由于 ICE 增加了成本,很多半导体供应商将更多除错硬体整合在晶片上,以解决除错限制的问题,并提供与 ICE 相似的功能。片上除错硬体的一种常见实现是飞思卡尔半导体公司在 68-kbit Coldfire 嵌入式处理器和 PowerPC(现在是 Power 架构)处理器上的背景除错模式(background debugger mode ,BDM)。其他供应商也有相似功能的专有名称。

片上除错硬体增加了一些功能,如硬体中断点、内部暂存器存取、读/写到记忆体,以及观察点(watchpoint)等,这些功能以前只能透过 ICE 使用。在一个多处理器 SoC 中,可以将每块晶片除错硬体连接到主 JTAG 控制器。不同供应商的连接可能有所不同,但典型的作法是在片上除错 JTAG 状态机和主除错器之间建立起一个 TDI-TDO JTAG 链(图 4)。

跟踪

即时系统除错中最大的问题之一就是海森堡的臭虫(Heisenberg bug),或探针效应(probe effect):为除错或监控而增加的任何软体或硬体都可能改变即时系统的行为。当增加用于剖析、除错或监控资讯的软体时,就会发生这种情况。使用除错硬体时也会有类似的影响。例如,片上除错硬体可能将处理器的执行流程修改到插入中断点处,或者用于剖析的硬体可能"偷取(steal)"从处理器到记忆体的部分频宽,以便用来保存剖析的资讯。

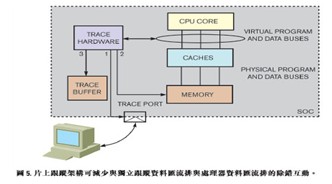

除错硬体还可能以 UART 连接来记录资讯,而产品软体也可能使用这个介面。ICE 通常提供非侵入式的跟踪功能,开发者可以在任何时候存取处理器的程式计数器。越来越多的 SoC 供应商正在把跟踪硬体整合到晶片上,以提供类似的功能(图 5)。

透过专用的跟踪硬体、专用的跟踪埠、跟踪资料与处理器资料分离的资料匯流排,以及 JTAG 介面,使跟踪硬体得以实现非侵入式的跟踪。

使用者可以利用一个跟踪埠来擷取跟踪资讯。在这种方式下,将一个跟踪盒或逻辑分析仪连接到跟踪埠,以重建资讯并让它们与原始码建立关联性。另一种擷取跟踪资讯的方法是使用一个虚拟跟踪缓衝记忆体,处理器记忆体将跟踪资讯存入缓衝记忆体,而当测试结束时由主机(例如透过 JTAG 埠)来检索(retrieve)这些资讯。第叁种方法是使用一个专用的跟踪缓衝记忆体,专门用来保存跟踪资讯,这可以让主机在测试结束时检索。

全球嵌入式处理器除错介面(Global Embedded Processor Debug Interface)的IEEE-ISTO 5001TM 2003 Nexus 5001TM 论坛标准可为嵌入式处理器的软体发展和除错提供一个开放而通用的介面(参考文献 7)。Nexus Forum 在 1998 年开始运作,在1999 年发表了第一个 Nexus 标准,并在 2003 年做了更新。其目标是,在嵌入式系统除错与

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)

- 嵌入式系统实时性的问题(06-21)

- 嵌入式实时系统中的优先级反转问题(06-10)

- 嵌入式Linux系统中MMC卡驱动管理技术研究(06-10)

- FPGA的DSP性能揭秘(06-16)