基于DSP的视频监控系统的硬件设计

成RGB(5:6:5)格式,然后利用2个SDRAM作为帧缓存,利用场间插值算法,完成隔行到逐行的转换,并将帧率由25 Hz提升到60 Hz,同时产生SVGA格式、帧频为60 Hz的行、场同步信号,并把被放大的图像数据经D/A转换后输出到VGA接口,VGA显示器上实时显示采集的图像。

2.4 外围接口模块

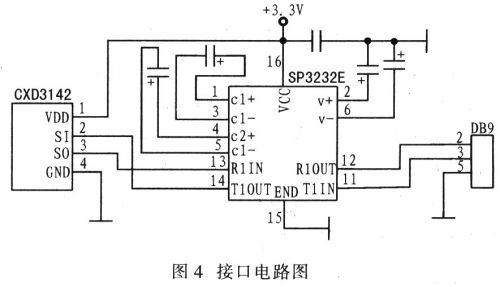

本设计支持RS-232C串口通信。但该串口通信需把3.3 V逻辑电平转化成RS-232C标准电平。因此采用SP3232E系列器件完成电平转换。SP3232E可从+3.0~+5.5 V的电源电压产生2Vce的RS-232C电压电平。该系列适用于+3.3 V系统。SP3232E器件的驱动器满载时典型数据速率为235 kb/s。图4为系统设计的接口电路图。

需要注意的是,由于采用SP3232E器件,其驱动能力有限,该接口电路只适用于近距离传输。如果要进行远距离传输,则必须加强信号传输能力。

3 系统硬件调试

系统硬件调试应先调试电源模块,如果系统电源错误,器件将损坏;然后调试DSP模块。DSP上电后,空闲情况下一般不会发热,若有轻微的发热情况应立即断开电源以免损坏DSP器件,其主要原因是把DSP的工作电压接到DSP的非电压引脚。DSP的工作电压正常后,再检查复位电路、时钟电路是否正确。如果DSP的时钟引脚无信号,一般是电路虚焊。如果有信号,但工作频率达不到系统工作的正常值,则通过调整外部可调电容。如果还达不到要求,则应考虑时钟信号是否受到低频信号干扰,就要认真检查电路板,必要时应修改布线。FPGA模块的调试与上述方法相同。

4 结论

该系统设计已成功应用于数字视频展台项目。目前该产品已投入生产,但图像质量还有待提高,可能是模拟视频信号失真和白平衡的值设置不恰当。该设计方案具有较强的灵活性,还可应用于监控、安防等产品开发。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)