基于DSP的光纤监控网络系统方案

0引言

中性束注入加速极电源是为国家大科学工程超导托克马克聚变实验装置(EAST)研制的一套高压大功率脉冲电源。此电源采用PulseStepModulaTION技术,用80个相同的1100v/100A输出的电源模块串联而成,其额定输出为:80kv/80A,最大脉宽1000s。由于该电源置于高压、强电磁干扰环境下,因此,为保证该电源系统的安全和稳定,须对各电源模块的状态进行实时监控。通过对各种方案的比较,采用计算机RS232口和DSP(DigitalSignalProcessor,数字信号处理器)的RS232口通过光纤转换器组建光纤环网。整个系统具有结构简单,性价比高,易扩充等优点。

1 光纤网络结构

1.1 光纤网络硬件

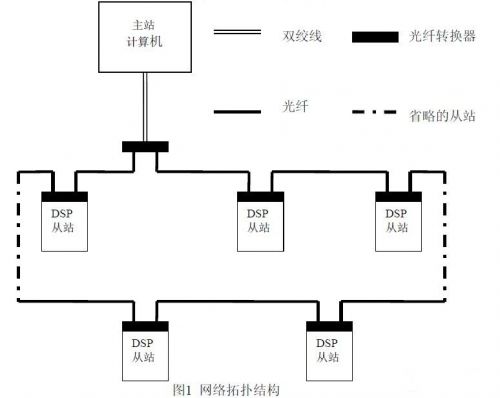

该光纤监控网络采用RS485总线的单主多从结构,主站用PC机,从站用DSP,采用多模光纤连接,组建成带双环自愈功能的光纤环网。带双环自愈功能光纤环网的优点是:当网络上某个节点的光纤转换器出现故障时,其它节点仍能正常通讯。光纤转换器采用武汉迈威公司生产的MWF5100P,它把RS232信号转换成统一的光信号传输。DSP采用TI公司的TMS320LF2407A。

主站串口COM1与各从站通讯,主站发出信号,从站经过判断决定是否要发送数据给主控计算机。当遇到故障时主站可以发出信号使所有的电源模块复位。网络拓扑结构见(图1)。

1.2 光纤网络软件

主站采用MSCOMM控件编写的WINDOWS系统的通讯界面,简单易用。可以根据需要设定不同的参数。从站采用TI公司针对TMS320C2XX开发的一套集成开发环境CC(CODECOMPOSE)。CC采用图形接口,提供编辑指令、参数修改工具,能对TMS320C2000系列DSP进行指令级的仿真和进行可视化的实时数据分析,可大大提高开发者的工作效率,缩短应用系统开发周期。

DSP多处理器通讯有两种方法:空闲线模式和地址位模式。由于地址位模式在高的发送速度下,程序速度不足以避免在传输流中的一个10bit的空闲,且空闲线模式与RS232通讯兼容,因此该光纤网络采用空闲线通讯模式。

主站通过COM1口与从站通讯,用软件中断的方法接收从站上传的信息。主站不管是接收还是发送的数据都是NRZ(非归零)格式的。NRZ的格式包括以下组成部分:一个起始位、1~8个数据位,一个奇偶校验位(可选)、1或2个停止位。

从站接收到一帧数据时,产生一个中断,并判断是否与自己的虚拟地址一致。主站与从站的设定如下:从站虚拟地址从01到80,当从站接收到的数据与自己的地址一致时,发送信息给主站,否则处于等待接收状态(图2),各从站之间不通讯,同一时刻只有一个从站发送信息给主站。DSP有一个RS232通讯口,程序通过接收中断、发送中断,接收指令和发送指令进行通讯。

从站能够通过程序设定波特率、奇偶校验位和数据位长度等通讯参数。

2 模拟调试

用一台PC机,2块合众达公司的SEED-DSK2407评估板,3个光纤转换器和多模跳线组建了一个光纤环网,对通讯时间进行了测试。测试仪器是泰克公司的TDS3032B示波器。用PC机COM1通讯口的3号引脚的第一个上升沿为触发信号,触发电平为5V。通讯时间测试过程如下:

COM1通讯口3号引脚发送数据的第一个上升沿作为起始时间,到2号引脚接收到从站上传数据的第一个上升沿为止,这个时间即为主站与从站一次通讯的时间。经多次测试,通讯没出现错误,一次通讯时间为560us(图3),波动在20us以内,数据的传输速度设定为9600bps。

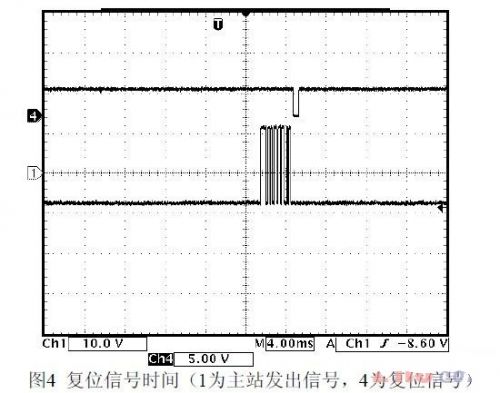

图3通讯时间波形图(1为发送,4为接收)复位信号时间的测量如下:采用PC机COM1口的3号引脚的第一个上升沿为起始时间(触发电平5V),到从站IOPF0引脚产生的第一个下降沿为止,这个时间即为从站复位的时间。经多次测量,平均复位时间为3.24ms左右(图4),波动在80us以内。

图4复位信号时间(1为主站发出信号,4为复位信号)经在9600bps,38400bps,115200bps三个不同传输速率下的测量,在程序调试成功的情况下,主站与从站之间的通讯一次就能建立,通讯不出现误码。之所以出现时间上的波动,是因为数据传输的路径和测量误差决定的。

光纤转换器的转换延时测试,由COM1通讯口的3号引脚触发信号,两块DSP的RS232口接收信号。测试结果是:经过一个光纤转换器延时为500ns。在以后实际的光纤网络中接80个光纤转换器,采用双环自愈方式的光纤环网,最长的一次通讯延时要经过40个光纤转换器,传输延时是20us,与一次通讯时间560us相比可以忽略。又因为采用的是异步串口通讯,所以20us的延时对网络通讯的影响很小,从监控角度考虑可以忽略。

3 结语

通过对多次测试结果的分析,监控系统的主站与其中一个从站通讯的平均时间

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)