基于DSP在捷联惯性制导技术中的应用

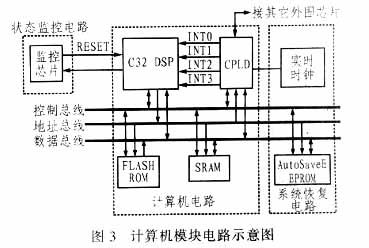

系统中的计算机模块电路一般由状态监控、系统恢复和计算机电路组成。本模块电路示意图见图3所示。该模块是全系统的核心,而C32 DSP更是核心中的核心。因此,有必要对其进行专门的监控,以保证其正常运行。设计时可通过状态监控电路来对C32 DSP和电源进行监控,以防因偶然情况出现死循环、程序偏离预定流程而导致系统失效。

惯性制导系统是历史信息敏感型系统,如果系统因故重启后没有历史信息,其后的导航计算就没什么意义。所以有必要对系统运行的一些重要信息进行保存,以便重启后能迅速接替以前的工作。为此,本系统采用了两条措施:第一是使用高速自动存储E2PROM对数据存储器中的重要数据进行自动备份;第二是使用一个具有备份电源的实时时钟芯片来记录从上一次导航数据保存时刻到重启后读取导航历史信息之间的时间长度。该实时时钟芯片在主电源掉电后能利用备份电源提供几十秒的电能。系统恢复电路就由上述两个芯片构成。

计算机电路是本模块的核心电路,它由C32 DSP、SRAM、FLASHROM和CPLD构成。为提高性能,该电路采用32位数据总线和24位地址总线。同时,由于C32被设置成了微机工作模式,因而具有自主引导功能。系统程序固化在FLASHROM中,SRAM则用作数据存储器。将CPLD作为C32和外围芯片的接口可实现很多逻辑电路功能。外围芯片与C32的连接需要有一个唯一的I/O地址,因此在CPLD中设计的I/O地址分配电路可为每个外围芯片分配一个I/O地址。另外,C32本身的外部中断源只有四级(个),而系统中需要通过中断来执行的程序又不止四个,故采用中断和查询相结合的办法来解决这个问题。由于同一级中断中包括好几个中断源,这样,在该级中断响应时再对具体的中断源进行查询即可确定需要具体响应哪个中断源。因此,在CPLD中设计了中断分配电路。对于启动和运行时间都很严格的中断源来说,可由各种频率的时钟信号来对其进行触发。所以,CPLD中还设计了时钟分频电路,即用系统的精确时钟来分频以产生所需的各种频率时钟。

对于I/O地址分配电路、中断分配电路和时钟分频电路,如果用标准逻辑器件(74系列或54系列)来实现,将需要很多芯片,这样一方面将使电路部分的体积和功耗增加;另一方面也会使电路的规模扩大、复杂性增加、可靠性下降。因此,这三个电路可用CPLD(复杂可编程器件)来实现。为了充分利用CPLD 的灵活性,系统中其它的一些逻辑电路也被放到这里。这样,在一片170mm×170mm的小芯片

中就可实现系统所需的大量逻辑功能。

3.3 系统程序设计

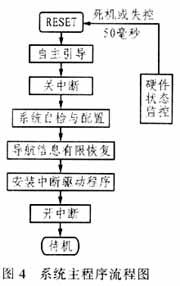

导航、制导计算都属于实时计算。要实现这一要求,软件就必须结合硬件来进行设计,以充分发挥硬件的功能。本设计充分利用了系统的中断功能,并以中断为主来进行程序设计,以使系统中各个部分的具体功能都可通过中断程序来实现。其系统工作过程如下:

加电开机→FLASH中的程序调入内存→系统初始化、自检→导航信息恢复→安装中断程序→打开中断→待机。

该系统的软件包括主程序、子程序和各中断响应程序等部分。

其中主程序是系统程序的框架,重要的初始化参数主要在主程序中定义,主程序通过调用子程序来完成系统初始化、自检、导航信息恢复、系统配置、中断程序配置等功能。其中,系统自检程序主要检测CPU、SRAM以及各接口芯片的工作是否正常。引导程序主要根据系统硬件中存储的状态信息来确定导航计算的起点。主要状态信息有:系统是加电开机还是死机后重新启动,以及上一次保存数据与当前的时间间隔等。根据系统硬件中保存的状态信息和非易失存储器中保存的导航信息可确定当前导航计算的基准点。系统主程序流程如图4所示。

子程序主要用来完成一些特定的功能,包括导航子程序、控制子程序、通讯子程序和卡尔曼滤波子程序等。

中断程序由硬件中断触发,除完成现场保护和硬件信息处理外,还可根据需要调用导航子程序、控制子程序、通讯子程序、状态监控子程序、卡尔曼滤波程序等,同时在处理完成后恢复现场并向主程序返回数据。

4 结束语

捷联惯性制导是一种很有应用价值的惯性制导方法,随着计算机技术的发展,该技术将迅速应用于各种战术武器中。本文并不企图在理论上进行创新,而是在技术上谋求好的实现方法。实验证明:用DSP芯片对惯性器件的信息进行处理,并用可编程器件进行逻辑电路的实现,可简化系统电路,提高系统的运算性能以及可靠性和灵活性。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)