基于DSP的卫星测控多波束系统设计

2.DSP模块结构 3.DSP模块设计的特点

接收卫星信号的阵列天线为6×6的面阵,多通道接收机完成信号的采样,再经过数字下变频,送到处理单元的是36个通道的I、Q两路共72路数据。由于阵列信号的数据量大,算法也比较复杂,我们需要使用2片TS101S芯片并行处理来实现。

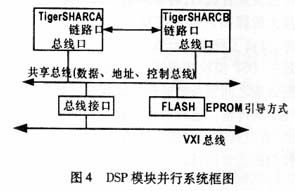

并行系统的互连结构包括2种方式:共享存储器结构和分布式结构。共享存储器结构的连接方式是将所有的处理器都连到一个通道上,该通道一般是一种背板总线(如VXI总线),它既可以作为处理器间的通信媒介也可以作为处理器和共享存储器间的数据通信。这种结构数据传输的带宽远远大于直接连接的通信端口,但是存在着总线竞争问题,随着处理器数目的增加,处理器平均的总线带宽会降低,影响数据吞吐量。分布式结构处理器之间通过链路口进行直接的数据传输,链路口在处理器之间提供了高宽带的点对点通信。这种连接完全为了处理器之间的通信,但是在数据传输时会占用其他DSP芯片的内部资源。

TigerSHARC DSP芯片硬件上可以同时支持这两种并行体系结构,前者通过共享外部地址数据控制总线方式实现,后者通过DSP间的专用的链路口点对点的互连实现。本文所设计的DSP模块结构从通信网络的连接关系来看,既是共享总线系统,又是分布式系统,两片DSP芯片的外部地址总线、数据总线、控制总线直接相连,并且一起通过总线接口连接到VXI总线上,实现和其他模块的数据通信。由于每片DSP内部有6 Mbit的双口RAM,因此不需要外部数据存储器。DSP A和DSP B的链路口也直接相连,两片DSP可以通过链路口交换数据。DSP模块程序采用EPROM方式引导,两片DSP共用一片548K×8bit的FLASH DSM2150作为程序存储器。DSP模块框图如图4所示。

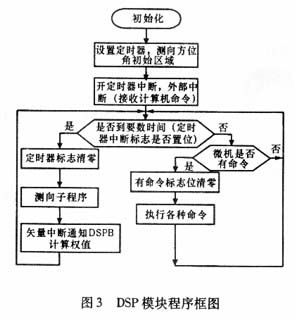

整个DSP模块的处理时间分为3个时间段,分别为从缓冲中读取数据时间、测向时间和波束合成权值计算时间,其中主要的开销是测向的时间。为了使DSP模块具备更高的效率,必须根据该模块的结构和Tiger DSP芯片的性能合理分配任务。由于主要的开销是测向算法,所以解决好测向的并行算法是尤其重要的。在MUSIC算法中,判断出信号个数后要分别对各个信号区域进行峰值搜索,最后锁定信号来向,系统最多可测4个不同来向的信号,因此将峰值搜索的区域划分后交给两片DSP同时进行搜索,可以节约大量的时间。测向和波束合成权值的计算不能同时进行,DSP A通知 DSP B进行波束合成后又可以返回去从缓存区中读取数据,此时DSP B计算波束合成的权值,这样又大大提高了并行度。控制终端对DSP模块的命令是通过外部中断读入,在执行控制终端的命令时将定时器时钟关闭。

DSP模块的程序框架用C语言来构建,在C中插入汇编来提高运算效率,并充分利用TigerDSP芯片双处理器核的SIMD结构,为了更好地对整个的程序进行优化,使用开发软件中的工具Linear profiling 分析各个子函数所占用的时间比例,从而优化程序的瓶颈。并行的系统设计和一些优化措施使DSP模块的运行时间能够满足系统设计的需求。

在卫星测控多波束系统DSP模块的设计中我们考虑了多方面的因素,可以归纳为以下几个特点:

首先,高性能TigerSHARC DSP并行结构保证了系统的性能,系统要求在500 ms内完成最多4个来波方向的测定和波束合成,使用两片Tiger SHARC DSP并行工作,在300 ms内就可以完成,使得系统有充裕的时间去响应控制终端的命令。

其次,性能优越的测向和波束合成算法保证了系统的稳定工作,测向的精度保证在0.5°范围内,信号经过波束合成后,将噪声信号加以抑制,信噪比有了很大的提高。并且在双DSP处理器中并行分配任务,提高了程序运行效率。

第三,DSP模块和波束合成模块之间以及和外部控制终端之间完备的通信协议保证了数据和命令能构准确的传输。这种通信协议是根据实际需要自定义的,并且具有一定的容错功能,保证了各个模块之间接口的正常运行。

最后,系统控制流程设计合理,我们使用了DSP的外部中断1、2、定时器中断,以及两片DSP之间通信的矢量中断来实现对系统的控制,为了使高速运行的DSP能够有效的与其他模块、外部控制终端进行通信,程序流程的设计经过了仔细的推敲,为DSP的稳定工作提供保障。

五、结束语

本文讨论了卫星测控多波束系统DSP模块中算法的并行实现以及并行处理任务的分配,采取了一系列措施优化DSP模块的整体程序,并应用了模块化的思想,结构设计合理,能够满足系统的需求。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)