基于TMS320C64x DSP/BIOSⅡ的嵌入式语音采集与盲分离系统设计方案

法作为一个线程插入队列,由DSP/BIOS II进行调度。

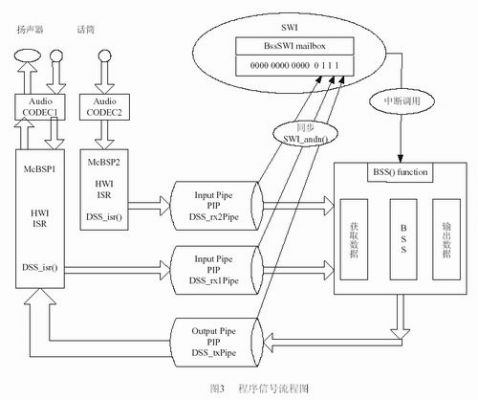

在本系统中,需要用DSP/BIOS II的配置工具来配置生成一个软件中断(BssSWI)、三个PIP对象(DSS_rx1Pipe、DSS_rx2Pipe和DSS_txPipe)、一个硬件中断(HWI)。BssSWI实现BSS。三个PIP对象完成与语音编解码芯片相连接的串口和软件中断之间的数据交换,语音编解码芯片采集到的两路语音数据流向串口,然后经DSS_rx1Pipe和DSS_rx2Pipe送到软件中断,软件中断对两路信号进行盲分离(BSS),然后将分离出来的信号DSS_txPipe送回串口ISR,最后送到语音编解码芯片输出。程序信号流程图如图3所示。

图中三个PIP对象中的DSS_rx2Pipe和DSS_rx1Pipe分别对应着SWI邮箱中的bit2和bit1,DSS_txPipe对应着SWI邮箱中的bit0,初始值均为1,通过这三位来实现同步。当ISR接收到一满帧信号,就会调用相应的SWI_andn( ) 来清除SWI 邮箱中的相应位(如DSS_rx1Pipe调用SWI_andn(1)来清除邮箱中的bit1)。而且, 当出现一个空的数据接收块时,将调用SWI_andn(0)来清除邮箱中的bit0。一旦bit2、bit1和bit0均为0时,触发BssSWI,就调用Bss( )来进行盲信号分离。

4 结束语

本文设计了一个高性能的、基于DSP/BIOS II的嵌入式混合语音信号的采集与盲分离系统,采集到的数据经过DSP的McBSP和EDMA通道直接被送到片内存储器堆栈中,然后进行BSS,将混合语音分离出来。系统还采用了实时操作系统DSP/BIOS II,大大地简化了编程的难度和提高了系统的实时性和稳定性。由于该系统结构简单、实时性好、性能稳定和易于集成,所以在移动通信终端有广泛的应用空间和良好的市场前景。

另外,由于BSS算法复杂,在一定程度上影响了整个系统的性能。因此,要想进一步提高系统的实时性,研究简单的、易于实现的、鲁棒性好的BSS算法是十分必要的,这也是我们的下一步工作。

DSP BIOS BSS TMS320C6416 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)