基于DSP的心电监护模块设计方案

心脏在机械收缩之前,心肌预先发生电的激动,并向全身各部位放散,从而在体表的不同部位产生电位差。通过体表把这种变动着的电位差按时间顺序描记出来的连续曲线就是心电图ECG。

心电图是诊断心律失常的最可靠的途径,其它临床检查虽然也可以诊断某些心律失常,但是准确率不高。通过观察患者的心电图,其诊断准确率几乎可以达到100%。心电监护模块的功能就是实时地记录下病人的心电波形,并进行自动分析和处理,同时给出相应的结论。

随着数字信号处理技术和大规模集成电路工艺的发展,单片数字信号处理器的功能越来越强大,价格越来越低,越来越多地被应用到人们生产生活的各个领域。本文介绍一种基于DSP芯片的心电监护模块的解决方案,讨论了它的硬件结构和软件组成。

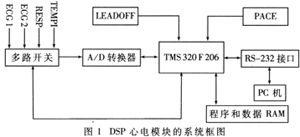

该心电监护模块是一个以美国德州仪器公司(TI)的TMS320F206为核心的DSP数据采集和处理模块。整个系统安装在一块4层的PCB板上,通过9针RS-232电缆和PC机进行通讯,其原理框图如图1所示。其中所有的输入信号包括ECG1、ECG2(两路心电信号)、TEMPI(体温信号)、RESP(呼吸信号)、LEADOFF(导联脱落检测)、PACE(起博器检测)等均来自心电信号前期模拟处理模块。

1 TMS320F206简介

TMS320F206(以下简称F206)是TI公司于1996年推出的一种性价比很高的16位定点DSP芯片,运算速度为40MIPS。F206体系采用改进的哈佛结构,将程序存储器和数据存储器的总线分开,以便最大限度地提高处理能力。其可寻址空间为224K字(64K字程序空间,64K字数据空间,64K字I/O空间,32K字全局空间),64K字程序空间中的前32K字可映射到F206片内集成的闪烁存储器(FLASH MEMORY)中,这样可以通过仿真器对F206进行在线的编程和擦写。F206片内具有4级流水线结构,其指令集专门对信号处理中常用的乘-加运算作了优化,支持单周期的乘法/累加指令;支持存储器块搬移指令,以便更好地管理程序和数据;支持基2的FFT位倒序检索寻址。

除支持高速运算以外,F206还具有众多的片上外设,主要包括:①软件可编程定时器;②用于程序、数据、I/O存储空间的软件可编程等待状态发生器,便于和低速器件接口;③片内振荡器和锁相环(PLL),用于时钟选择×1,×2,×4,÷2;④同步串口,便于和串行CODEC接口;⑤全双工的异步串口,便于和PC机通信。

2 硬件组成

该心电监护模块共有4路输入:两路心电信号ECG1和ECG2、一路体温信号TEMPI、一路呼吸信号RESP,采用分时采样的工作方式。由于呼吸信号和体温信号的频率远小于心电信号的频率,在确定采样率时就以心电信号为基准。经验表明,在做常规心电图时,要求系统的带宽为100Hz左右,根据Nyquist采样定理,采样频率必须不低于200Hz。考虑到一定的工作裕量,每个工作通道的采样率取250Hz,这样对4个通道而言,总的工作频率为1kHz。通道切换的工作由一片双向模拟开关CD4051来实现,将C、B、A控制端连接到TMS320F206的三根地址线上,通过I/O指令打开相应的模拟通道,进行信号的采样。

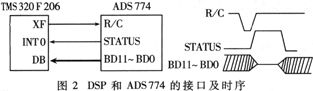

信号的采样和量化工作由一片ADS774完成。ADS774是美国Burr-Brown公司生产的12位逐次逼近型并行A/D转换器,典型转换时间为8.5μs,并且有多种工作方式可供用户选择。在本心电模块中我们选用了直通 throughout 模式,仅用两根控制线R/C和STATUS与TSM320F206接口,其工作原理和时序如图2所示。

TMS320F206通过指令在XF引脚上产生一个宽度大于25ns的低电平脉冲,启动ADS774进行一次转换。启动后ADS774的STATUS引脚变为高电平,转换结束后ADS774数据线上的数据有效,此时其STATUS引脚跳变回低电平,通过这个电平跳变触发TMS320F206的INT1外部中断,将12位转换数据读入数据存储器。

由于TMS320F206片内的数据存储空间有限,为保存大量的采样数据和运算的中间结果,需增加外部数据存储器;同时为了在调试程序时能够设置断点和进行单步操作,也需要增加外部程序存储器。我们采用了4片日立公司的8位SRAM HM62256-10,两两组成16位的程序存储器和数据存储器,分别用F206的PS和DS信号进行片眩HM62256-10的典型存取时间为100ns,而TMS320F206的指令周期为50ns。为节省硬件等待电路的开支,利用了TMS320F206片内的可编程软件等待状态发生器产生两个等待状态,从而满足存储器的操作时间要求。利用TMS320F206片上集成的全双工异步串口,可以实现心电模块和PC机的通信。但是RS232电平和TTL电平不兼容,我们使用了一片电平转换芯片MAX202,它采用+5V单电源供电,使用时只需加几个电容,便能完成两种电平的转换。为防止数据在传输过程中受到干扰,

DSP 心电监护 TMS320F206 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)