基于DSP+DUC的短波阵列信号发生器设计

单的配置,如采样率、数据格式等,并配置自身的接收串口,设置为链式DMA方式,从而在一块指定的内存区间不间断地重复存储和刷新音频采样数据;

其次,DSP将对DMA存储空间的数据作数字调制运算,载波信号使用的是预制的几组较低频率(如5 kHz、10 kHz等)的余弦信号之一;然后对已调数字信号根据不同的阵列流型添加不同的幅度、相位差,构成带有幅度和相位差别的阵列信号;最后将阵列信号数据按照不同的端口地址,以并行的方式写入FPGA中各自对应的暂存FIFO中,由FPGA负责将其分配至各个DUC数据端口;

再次,DSP对9个DUC内部寄存器的配置,包括上变频倍数、输出载波频率、频谱搬移方式、输出模拟信号幅度等。DSP对于DUC的配置是以向不同地址的外部端口写入并行数据字的方式进行的,再通过FPGA的数据转换功能转变为串行SPI数据格式,分别对每个DUC作寄存器配置。

2.FPGA程序

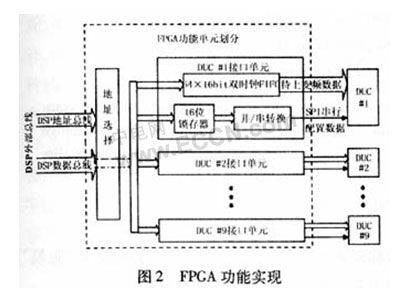

FPGA的功能是实现DSP与9个DUC之间的数据格式转换和分发工作,如图2所示,FPGA根据不同地址将DSP数据总线转送到不同的DUC(#1~#9)接口单元。

对于DUC配置数据,每个DUC接口单元先将其锁存,再对锁存数据作并/串转换,转变为SPI形式串行数据后,分别对每个DUC进行其内部寄存器设置。

对于待上变频数据,每个DUC接口单元都先将其送入一个64×16 bit的双时钟FIFO中,然后9个DUC同一时刻将各自的待上变频数据分别从FIFO中读出,作DUC运算,并以模拟信号输出。

五、结束语

本文所介绍的短波阵列信号发生器已用于实际短波测向系统的实验室验证,其多路短波阵列模拟信号输出可直接送入短波多波道接收机。

由于本信号发生器共有9路输出,因此可适用于9元及9元以下的各种阵型天线阵信号的模拟。通过对于信号发生器中DSP程序的选择,可选择所要模拟的阵型,并设置所希望的来波方向,从而产生带有阵型幅度和相位信息的多路阵列信号,提供给DSP算法的实际验证环境。

目前已测试了常用的直线阵、方阵(3×3,2×2)、圆阵(均匀,非均匀)等多种阵型,试验结果都达到了预期效果。

另外,本设计对外部双声道音频采样,可通过在左右声道上加上不同的音频信号,从而得到2个不同的调制信号,在DSP程序中将两者叠加,就可模拟短波测向中常遇到的同频多个信号的情况,用于验证测向算法对于同频多信号的区分能力。

在阵列信号处理机的调试过程中,短波阵列信号发生器的应用,极大地方便了短波频段阵列信号处理设备的实验室研制和调试,使得设备的外场调试时间大幅度缩短。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)