基于DSP的视频图像压缩系统的设计方案

时间:05-25

来源:3721RD

点击:

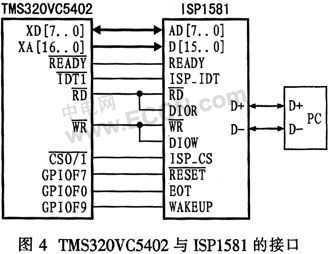

存器单元,使用8位地址线,可直接与TMS320VC5402地址线的低8位连接,使用CSO片选空间。因为ISP1581相对TMS320VC5402来说是低速设备,所以在应用中使用了READY接口信号。

TMS320VC5402具有丰富的I/O口资源,与ISP1581的控制信号接口十分方便。在设计中,选择TMS320VC5402的GPIOF7产生ISP1581的复位信号,在需要ISP1581复位时,产生一个宽度大于500μs的低电平脉冲。采用GPIOF0和GPIOF9控制EOT和WAKEUP,执行相应的功能。TMS320VC5402和ISP1581及PC的接口电路如图4所示。

4 软件系统设计

本系统的主要功能是对监控现场的全电视信号进行实时采样,然后对图像数据进行编码压缩并通过USB总线将图像数据传送给主机。

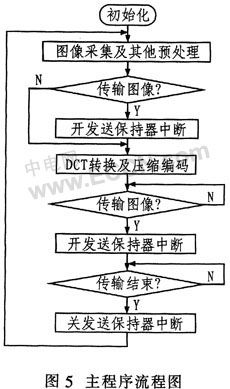

系统的主程序流程如图5所示,可分为初始化、图像采集、压缩编码和数据传输4个主要模块。

系统上电或复位后,DSP在收到主机的命令之前按缺省模式执行图像采集和编码压缩,收到主机命令后按命令要求执行图像采集和编码压缩;在图像采集和压缩编码过程中,DSP不停地检测总线,以便及时正确地发现主机命令。DSP接收到主机命令后,应尽快发送图像压缩数据,以尽量减少主讥的等待时间。

5 结束语

实践证明:本系统具有成本低、编程灵活和可靠性高等优点。而且压缩板体积小,便于携带安装,能在脱机状态下很好地完成图像压缩;利用TMS320VC5402获得了很高的图像处理速度和图像质量;利用USB2.0技术实现了图像数据的高速传输。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)